# AX99100 PCIe to Multi I/O Controller

#### Features

#### PCI Express

- Single-lane (X1) PCI Express End-point Controller with PHY integrated

- Compliant with PCI Express 2.0 Gen 1

- Compliant with PCI Express card specifications

- Compliant with PCI Power Management 1.2

- Supports four PCI Express functions

- Supports both legacy and MSI Interrupts

- Supports ASPM Power Management

#### Serial Port Interface

- Dual or Quad UARTs

- Supports RS-232/RS-422/RS-485 multiprotocol

- Bi-directional speeds up to 25 Mbps per port

- Full Serial Modem Control

- Supports Hardware, Software Flow Control

- Supports 5, 6, 7, 8 and 9-bit Serial format

- Supports Even, Odd, None, Space and Mark parity

- Supports Custom baud rate by internal PLL or external clock

- Supports On Chip 256 Byte depth FIFOs in Transmit, Receive path of each Serial Port

- Supports remote wakeup and power management features

- Serial Port transceiver shutdown support

- Supports Slow IrDA mode (up to 115200bps) on all Serial Ports

- Supports multi-drop application for 9-bit mode

- Supports DMA burst transfer

#### Parallel Port

- Compatible with IEEE 1284 SPP/Byte/ECP Mode

- SPI Master Interface

- Programmable SPI clock frequency up to 42MHz

- Supports Mode 0, Mode 1, Mode 2 and Mode 3 timing modes

- Supports MSB/LSB first transfer fashion

- Programmable peripheral chip select, selecting up to 7 SPI devices

- Supports Non-Burst-Type transfer up to 8 bytes and/or Burst-Type transfer via DMA mode for high performance

Supports to fragment large data block into several

Document No: AX99100/V0.24/06/06/16

- smaller transfers on SPI bus to reduce software loading

Supports programmable transfer 0 ~ 8 bytes

- OP-Code field in each transfer automatically to reduce software loading

- Supports wakeup by SWAKEn pin from Slave

#### Local Bus Interface

- Supports memory or I/O access through PCIe BAR0/1 to local bus interface, each BAR mapping to local bus' chip select (CS0n and CS1n)

- Supports direct access and bus master access (auto-increment and fixed address)

- Supports 8-bit or 16-bit data bus width (little and big endian bus swap)

- Supports up to 2 Kbytes address space and 2 chip select outputs when separated address/data bus style

- Supports up to 64 Kbytes address space and 2 chip select outputs when multiplexed address/data bus style

- Supports programmable local chip select region

- Supports "Slave Request based DMA" access for interfacing with external device with bus master

- Supports clock out, CLKO, up to 62.5MHz

- Supports asynchronous or synchronous Local Bus with required clock output, CLKO

- Supports programmable bus access cycles, self-terminated bus access cycles and back-to-back turnaround cycles

- Supports programmable RSTO, ALE, RDY, DREQ0/1, DACK0/1, CLKO polarity, and INT0/1 level/edge trigger

- Supports wakeup by INT0/1 and DREQ0/1 pins

- Supports I<sup>2</sup>C Master Interface

- Up to 24 bi-directional GPIO lines including 8 dedicated GPIO and 16 multi-function GPIO

- Integrates on-chip power-on reset circuit

- On Chip 3.3 to 1.2V Regulator

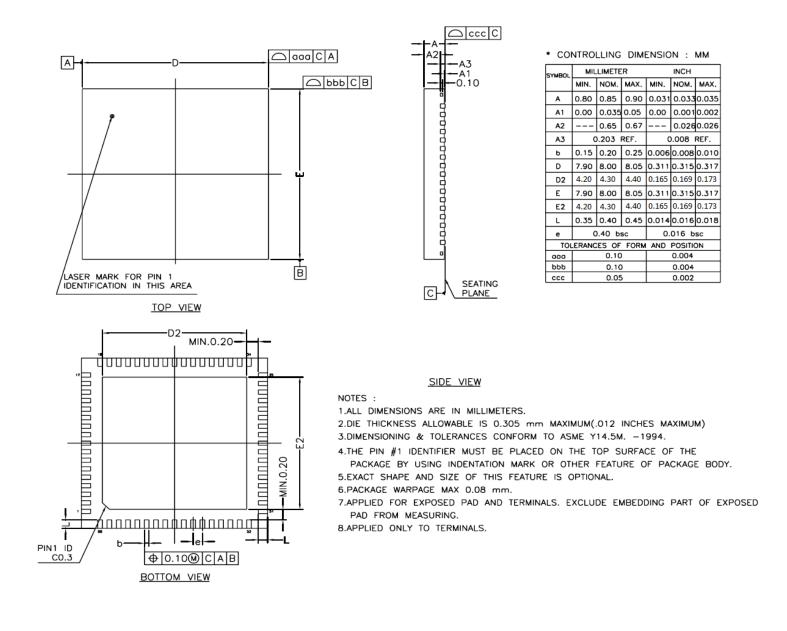

- 68-pin QFN RoHS compliant package

- Operating temperature range: 0 to 70°C or -40 to +85°C

#### **Product Description**

The AX99100 is a single chip solution that fully integrates PCIe 2.0 Gen 1 end-point controller and SerDes with a variety of peripherals such as four High Speed Serial Ports, one Parallel Port, I<sup>2</sup>C Master, High Speed SPI, Local Bus (ISA-Like), and GPIOs. It consists of four main configurations such as 4S (PCIe to Quad Serial), 2S+1P (PCIe to Dual Serial and Single Parallel), 2S+SPI (PCIe to Dual Serial and SPI), and LB (PCIe to Local Bus/ISA-Like) for different kinds of applications.

The AX99100, in 68-pin QFN, are available with RoHS compliant package and supports commercial grade operating temperature range from 0 to  $70^{\circ}$ C and industrial grade from -40 to  $85^{\circ}$ C.

#### **Target Applications**

2 Copyright © 2016 ASIX Electronics Corporation. All rights reserved.

Copyright © 2016 ASIX Electronics Corporation. All rights reserved.

#### DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "Reserved", "Undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

#### TRADEMARKS

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

# **Table of Contents**

| 1 | INTRODUCTION                                                       | •••• | 6  |

|---|--------------------------------------------------------------------|------|----|

|   | 1.1 General Description                                            |      | 6  |

|   | 1.2 AX99100 BLOCK DIAGRAM                                          |      |    |

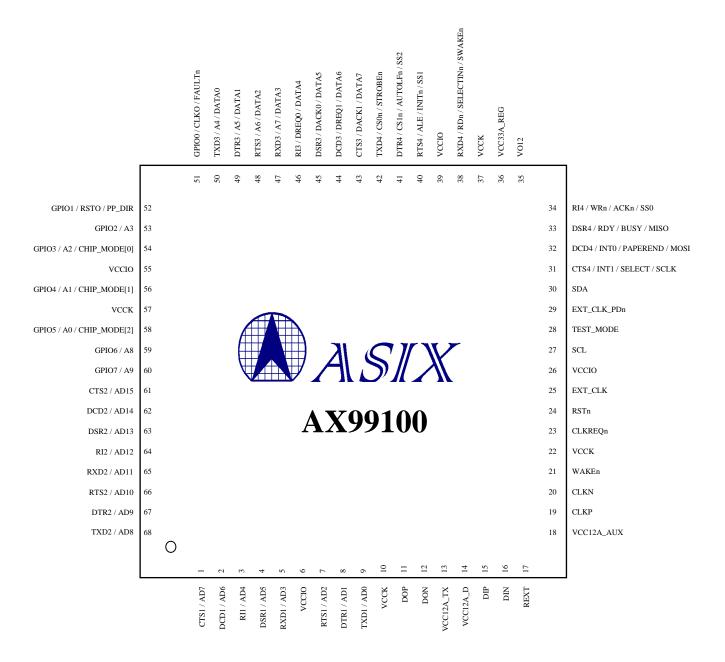

|   | 1.3 AX99100 PINOUT DIAGRAM                                         |      | 8  |

|   | 1.4 SIGNAL DESCRIPTION                                             |      | 9  |

|   | 1.4.1 GPIO and Mode Setting                                        | 1    | 1  |

|   | 1.4.2 Serial Interface for COM Port                                | 1    | 2  |

|   | 1.4.3 Serial Interface for Multi-Protocol Transceiver              | . 1  | 3  |

|   | 1.4.4 Serial Port with GPIO enabled                                | 1    | 4  |

|   | 1.4.5 Serial Port with Function Disabled                           | . 1  | 5  |

|   | 1.4.6 Parallel Port                                                | . 1  | 6  |

|   | 1.4.7 SPI Interface                                                |      |    |

|   | 1.4.8 Local Bus Interface                                          | . 1  | 8  |

| 2 | FUNCTION DESCRIPTION                                               | 1    | 9  |

|   | 2.1 Clocks/Resets and Power                                        | 1    | 9  |

|   | 2.2 PCIE OPERATION                                                 |      |    |

|   | 2.3 $I^2C$ Controller                                              |      |    |

|   | 2.4 SERIAL PORT (SP)                                               |      |    |

|   | 2.5 PARALLEL PORT (PP)                                             |      |    |

|   | 2.6 SPI MASTER CONTROLLER (SPI)                                    |      |    |

|   | 2.7 LOCAL BUS CONTROLLER (LB)                                      |      |    |

|   | 2.8 GPIO FUNCTION                                                  |      |    |

|   | 2.9 Power Management                                               |      |    |

| 3 | CHIP CONFIGURATION                                                 | 2    | :5 |

|   | 3.1 BOOT STRAPPING PINS FOR CHIP MODE                              | h    | 5  |

|   | 3.2 DTR BOOT STRAPPING PINS FOR SERIAL PORT                        |      |    |

|   | 3.3 HARDWARE CONFIGURATION EEPROM                                  |      |    |

|   | 3.3.1 Configuration EEPROM Memory Map for None Local Bus Interface |      |    |

|   | 3.3.2 Configuration EEPROM Memory Map for Local Bus Interface      |      |    |

|   | 3.3.3 Hardware Default Values Summary                              |      |    |

|   | 3.3.4 Disable Unused PCIe Function in HWCFGEE                      |      |    |

|   | 3.4 PCIE CONFIGURATION SPACE MAP                                   |      |    |

|   |                                                                    |      |    |

| 4 | ELECTRICAL SPECIFICATIONS                                          |      |    |

|   | 4.1 DC CHARACTERISTICS                                             |      |    |

|   | 4.1.1 Absolute Maximum Ratings                                     |      |    |

|   | 4.1.2 Recommended Operating Condition                              |      |    |

|   | 4.1.3 Leakage Current and Capacitance                              |      |    |

|   | 4.1.4 DC Characteristics of 3.3V with 5V Tolerant I/O Pins         |      |    |

|   | 4.1.5 DC Characteristics of Voltage Regulator                      |      |    |

|   | 4.2 PCIE SPECIFICATIONS                                            |      | -  |

|   | 4.3 POWER CONSUMPTION                                              |      |    |

|   | 4.4 POWER–UP/DOWN AND POWER MANAGEMENT SEQUENCE                    |      |    |

|   | 4.5 AC TIMING CHARACTERISTICS                                      |      |    |

|   | 4.5.1 PCIe Reference Clock Timing                                  |      |    |

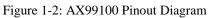

|   | 4.5.2 <i>I<sup>2</sup>C Timing</i>                                 |      |    |

|   | 4.5.3 Serial Port Timing                                           |      |    |

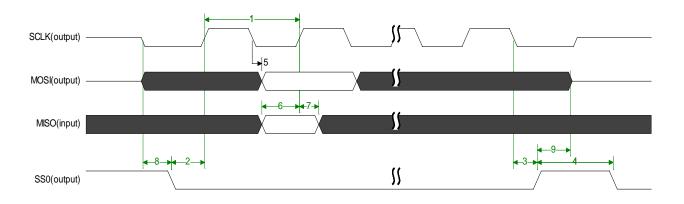

|   | 4.5.4 SPI Timing                                                   |      |    |

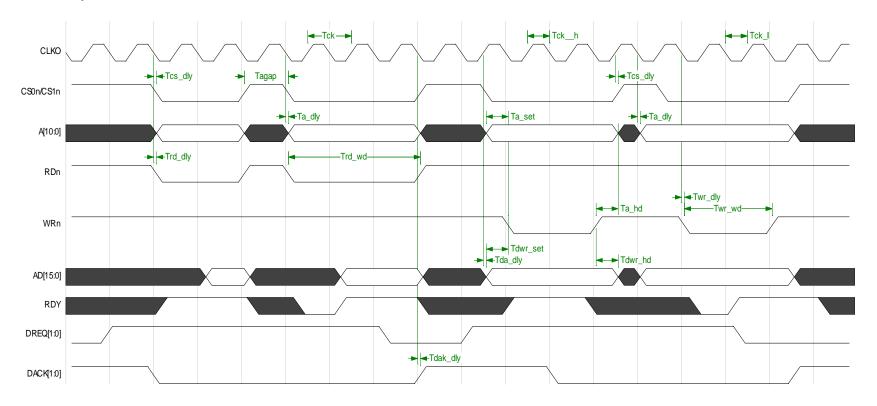

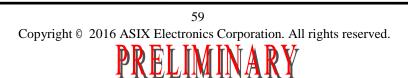

|   | 4.5.5 Local Bus Timing                                             |      | 9  |

| 5 | PACKAGE INFORMATION                                                | 6    | 8  |

| 6 | ORDERING INFORMATION                                               | 6    | 9  |

| 2 | 4                                                                  |      | -  |

Copyright © 2016 ASIX Electronics Corporation. All rights reserved.

# PRELIMINARY

# AX99100 PCIe to Multi I/O Controller

## **List of Figures**

| FIGURE 1-1: AX99100 BLOCK DIAGRAM                                             | 7  |

|-------------------------------------------------------------------------------|----|

| FIGURE 1-2: AX99100 PINOUT DIAGRAM                                            | 8  |

| FIGURE 4-1: TXD1 AND RXD1 TIMING DIAGRAM                                      | 57 |

| FIGURE 4-2: HIGH SPEED SPI MASTER CONTROLLER TIMING DIAGRAM AND TABLE         | 58 |

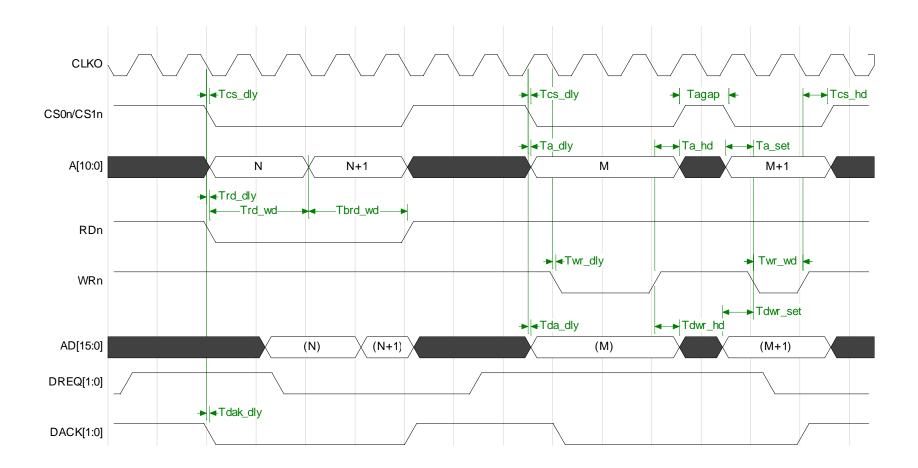

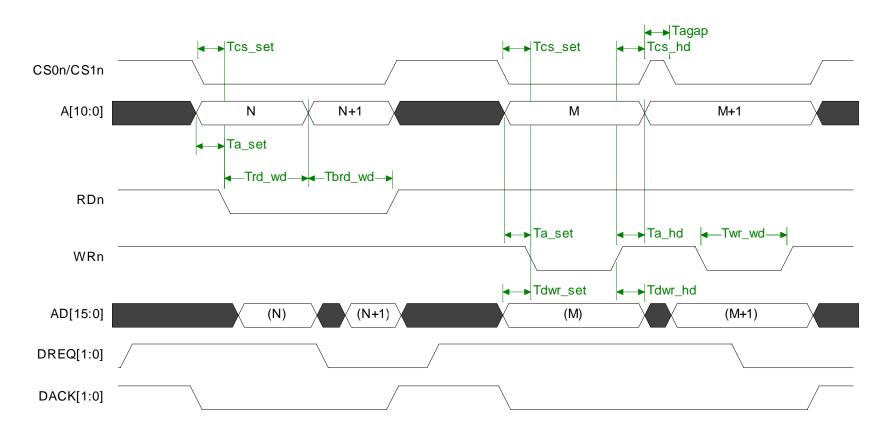

| FIGURE 4-3: NON-MULTIPLEXED BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM         | 59 |

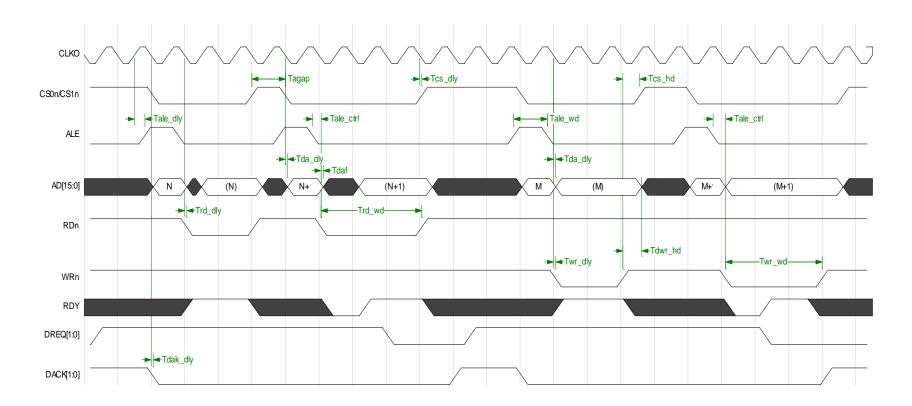

| FIGURE 4-4: ISA-LIKE BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM                | 60 |

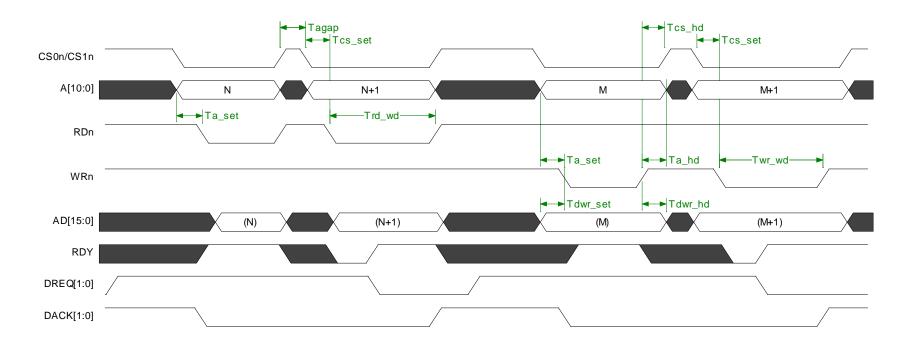

| FIGURE 4-5: NON-MULTIPLEXED BUS TYPE WITH INTERNAL CYCLE COUNT TIMING DIAGRAM | 61 |

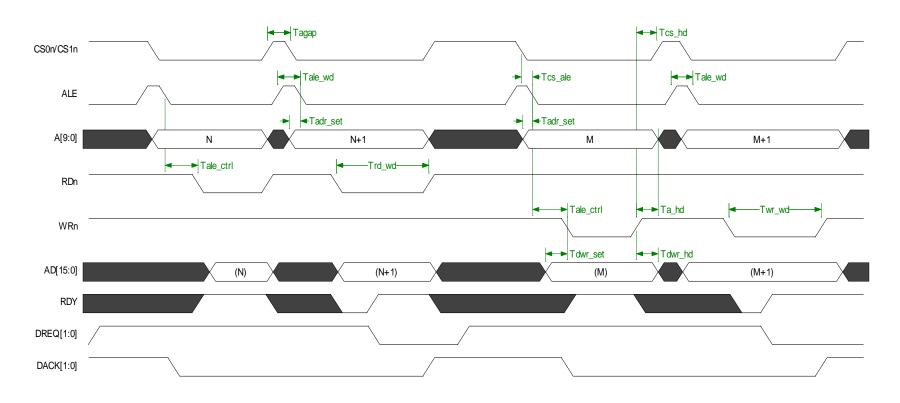

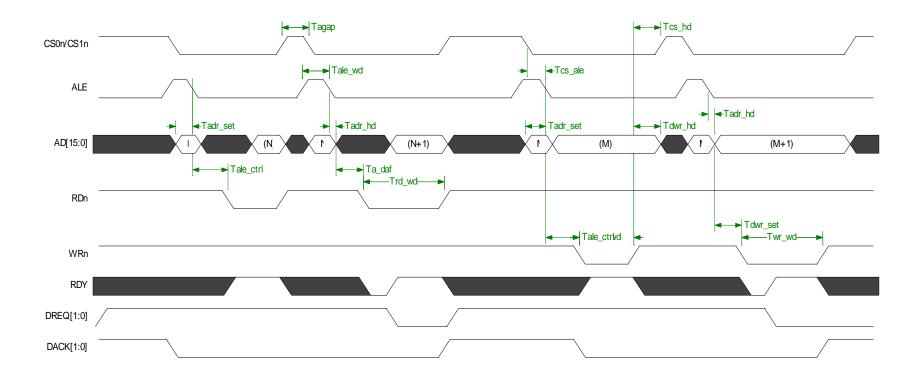

| FIGURE 4-6: MULTIPLEXED BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM             | 62 |

| FIGURE 4-7: NON-MULTIPLEXED BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM         | 63 |

| FIGURE 4-8: ISA-LIKE BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM                | 64 |

| FIGURE 4-9: NON-MULTIPLEXED BUS TYPE WITH INTERNAL CYCLE COUNT TIMING DIAGRAM | 65 |

| FIGURE 4-10: MULTIPLEXED BUS TYPE WITH EXTERNAL RDY TIMING DIAGRAM            | 66 |

|                                                                               |    |

## **List of Tables**

| TABLE 1-1: COMMON PIN DESCRIPTION                                          |    |

|----------------------------------------------------------------------------|----|

| TABLE 1-2: PCIE PIN DESCRIPTION                                            |    |

| TABLE 1-3: POWER/GROUND PIN DESCRIPTION                                    | 10 |

| TABLE 1-4: GPIO AND MODE SETTING PIN DESCRIPTION                           | 11 |

| TABLE 1-5: SERIAL INTERFACE FOR COM PORT PIN DESCRIPTION                   | 12 |

| TABLE 1-6: SERIAL INTERFACE FOR MULTI-PROTOCOL TRANSCEIVER PIN DESCRIPTION | 13 |

| TABLE 1-7: SERIAL INTERFACE FOR GPIO ENABLED PIN DESCRIPTION               | 14 |

| TABLE 1-8: SERIAL INTERFACE WITH PORT2 AND PORT4 DISABLED PIN DESCRIPTION  |    |

| TABLE 1-9: PARALLEL PORT PIN DESCRIPTION                                   |    |

| TABLE 1-10: SPI PIN DESCRIPTION                                            | 17 |

| TABLE 1-11: LOCAL BUS PIN DESCRIPTION                                      |    |

| TABLE 3-1: CHIP MODE SELECTION PINS                                        |    |

| TABLE 3-2: CHIP MODE SELECTION TABLE                                       | 26 |

| TABLE 3-3: DTR MODE SELECTION PINS                                         | 26 |

| TABLE 3-4: CONFIGURATION EEPROM MEMORY MAP FOR NONE LOCAL BUS MODE         | 28 |

| TABLE 3-5: CONFIGURATION EEPROM MEMORY MAP FOR LOCAL BUS                   |    |

| TABLE 3-6: HARDWARE DEFAULT VALUES IN EACH CHIP_MODE SETTING               | 43 |

| TABLE 3-7: THE HWCHGEE CONTENT FOR 1S SETTING                              | 46 |

| TABLE 4-1: I <sup>2</sup> C MASTER CONTROLLER TIMING TABLE                 | 56 |

| TABLE 4-2: LOCAL BUS TIMING TABLE                                          | 67 |

|                                                                            |    |

## **1 Introduction** 1.1 General Description

AX99100, PCI Express to Multi-I/O Controller, is a single chip solution for PCI express-based high performance Serial, Parallel port, SPI and Local Bus connectivity. It provides rich features and highly configurability for variety products.

AX99100 is a fully integrated, single-lane PCI express end-point controller and SerDes with rich high performance peripherals such as four High Speed Serial Ports, one Parallel Port, I<sup>2</sup>C Master, one High Speed SPI and Local Bus interface. AX99100 also provides rich GPIO ports can be controlled by software driver for some automation control applications.

The High Speed Serial Ports with the throughput up to 25Mbps, it can works with RS-232/RS-422/RS-485 multi-protocol transceivers and allow easy reconfigured Full/Half-duplex, Loopback and Termination resistors by software. The Parallel Port is compatible with IEEE 1284 and supports SPP, Nibble, Byte and ECP modes. An I<sup>2</sup>C interface is provided to configure AX99100 device options through an external EEPROM after chip reset and also supports to access other I<sup>2</sup>C device. SPI master provides a full-duplex, synchronous serial communication interface (4 wires) to flexibly work with numerous SPI peripheral devices. Local Bus interface provides configurable asynchronous or synchronous, 8 or 16 bits data bus width with specified endian type and address/data multiplexed or separated bus type access mode to support variety slave interface access types. All the GPIO pins are programmable and can be used as Input or Output. AX99100 supports 8 dedicated GPIO and every serial port pins can be configured as GPIO by software.

Generally, the clock source of AX99100 is from PCIe slot. AX99100 don't need any other clock source for the main operations. But AX99100 still supports a clock input from external oscillator for those special baud rate generated for UART, SPI and Local Bus used. AX99100 also integrates power-on reset circuit and 3.3V to 1.2V voltage regulator on-chip to provide simplifies reset and power supply for the core power of the chip. It supports single power operation and reduces the overall BOM cost.

AX99100 is available in 68-pin QFN RoHS compliant package and supports commercial grade operating temperature range from 0 to 70 °C and Industrial grade operating temperature range from -40 to 85 °C.

AX99100 provides cost effective solution to enable simple, easy, and low cost integration capability for PCIe to rich interface conversion applications. It could also provide highly programmable flexibility and compatibility for many applications such as serial, parallel and Bridge for home automation and Industrial control.

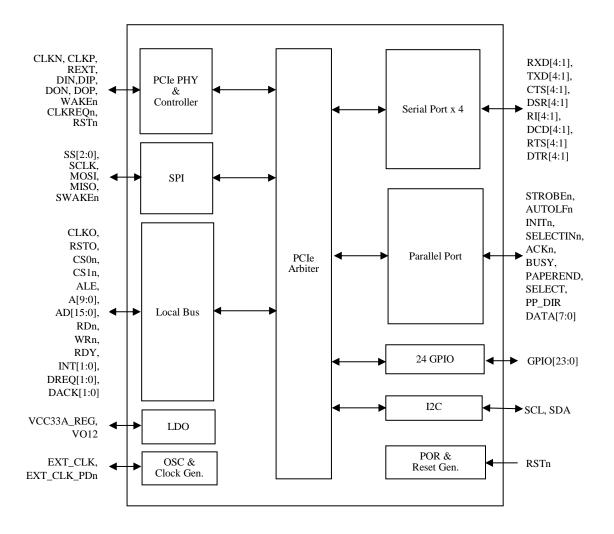

## 1.2 AX99100 Block Diagram

Figure 1-1: AX99100 Block Diagram

## 1.3 AX99100 Pinout Diagram

AX99100 is housed in a 68-pin QFN package.

8 Copyright © 2016 ASIX Electronics Corporation. All rights reserved.

## 1.4 Signal Description

Following abbreviations are used in "Type" column of following pin description tables. Note that some I/O pins with multiple signal definitions on the same pin may have different attribute in "Type" column for different signal definition.

| AB        | Analog Bi-directional I/O                 | 05         | Output, 3.3V with 5V tolerant |

|-----------|-------------------------------------------|------------|-------------------------------|

| AI        | Analog Input                              | PU         | Internal Pull-Up (75K)        |

| AO        | Analog Output                             | PD         | Internal Pull-Down (75K)      |

| <b>B3</b> | Bi-directional I/O, 3.3V                  | CU         | Controllable internal Pull-Up |

| B5        | Bi-directional I/O, 3.3V with 5V tolerant | Р          | Power and ground pin          |

|           |                                           | S          | Schmitt Trigger               |

| I3        | Input, 3.3V                               | Т          | Tri-state                     |

| 15        | Input, 3.3V with 5V tolerant              | <b>4</b> m | 4mA driving strength          |

| 03        | Output, 3.3V                              | 8m         | 8mA driving strength          |

For example, pin 5 in AX99100 package can be RXD1 or AD3. If RXD1 is selected, its Type is I5/PU; if AD3 is selected, its Type is B5/4m. In other words, the PU (internal pull-up) only takes effect in RXD1 signal mode while AD3 signal mode doesn't. User should refer to the table specific to desired function for exact pin type definition.

The multi-function pin settings are configured by pin 54, 56 and 58 to decide the chip operating mode. Please reference to Section 3 in detailed. The following abbreviations are used in pin description tables.

**HWCFGEE** I<sup>2</sup>C Hardware Configuration EEPROM

**CHIP\_MODE** Chip Operating Mode, Setting by external pull the pin 54, 56 and 68

| Common Pins |        |        |                                                                                  |  |  |

|-------------|--------|--------|----------------------------------------------------------------------------------|--|--|

| Pin Name    | Туре   | Pin No | Pin Description                                                                  |  |  |

| TEST_MODE   | I5/PD  | 28     | Test Mode enable. For normal operation, please always tie to logic low or NC.    |  |  |

| EXT_CLK     | I5     | 25     | External Clock Input from external Oscillator.                                   |  |  |

| EXT_CLK_PDn | B5     | 29     | External Clock Power Down enable.                                                |  |  |

|             |        |        | 0: Power down external Oscillator.                                               |  |  |

|             |        |        | 1: Enable external Oscillator.                                                   |  |  |

|             |        |        | Note: When external Oscillator existed, this pin should be pull down by external |  |  |

|             |        |        | resistor for boot strapping latch. Otherwise, please pull-up by external         |  |  |

|             |        |        | resistor to indicate NO external Oscillator existed.                             |  |  |

| SCL         | O5/T/4 | 27     | I <sup>2</sup> C Serial Clock line for I <sup>2</sup> C master controller.       |  |  |

|             | m      |        | SCL is a tri-stateable output, which requires an external pull-up resistor.      |  |  |

| SDA         | B5/T/4 | 30     | I <sup>2</sup> C Serial Data line for I <sup>2</sup> C master controller.        |  |  |

|             | m      |        | SDA is a tri-stateable output, which requires an external pull-up resistor.      |  |  |

#### Table 1-1: Common Pin Description

#### Table 1-2: PCIe Pin Description

|          | PCIe interface |        |                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | Туре           | Pin No | Pin Description                                                                                                                                                                                                                                                                                      |  |  |  |

| CLKN     | AI             | 20     | PCIe PHY differential PLL reference clock.                                                                                                                                                                                                                                                           |  |  |  |

| CLKP     | AI             | 19     | PCIe PHY differential PLL reference clock.                                                                                                                                                                                                                                                           |  |  |  |

| REXT     | AO             | 17     | Bandgap External Resistor<br>Connect this pin to ground through an external resistor of $20K\Omega$ , $\pm 1\%$ . The total<br>parasitic capacitor of this pin to ground must be less than 10 pF                                                                                                     |  |  |  |

| DIN      | AI             | 16     | PCIe PHY differential negative serial data input.                                                                                                                                                                                                                                                    |  |  |  |

| DIP      | AI             | 15     | PCIe PHY differential positive serial data input.                                                                                                                                                                                                                                                    |  |  |  |

| DOP      | AO             | 11     | PCIe PHY differential positive serial data output.                                                                                                                                                                                                                                                   |  |  |  |

| DON      | AO             | 12     | PCIe PHY differential negative serial data output.                                                                                                                                                                                                                                                   |  |  |  |

| WAKEn    | O5/T/4m        | 21     | An open-drain, active low signal that is driven low by a PCI Express function to reactivate the PCI Express Link hierarchy's main power rails and reference clocks.                                                                                                                                  |  |  |  |

| CLKREQn  | O5/T/4m        | 23     | Reference clock request signal<br>This pin is an open drain, active low signal that is driven low by the PCI Express<br>Mini Card function to request that the PCI Express reference clock be available<br>(active clock state) in order to allow the PCI Express interface to send/receive<br>data. |  |  |  |

| RSTn     | I5/PU/S/<br>4m | 24     | Active low asynchronous reset from PCIe.<br>Indicates when the applied main power is within the specified tolerance and<br>stable.                                                                                                                                                                   |  |  |  |

#### Table 1-3: Power/Ground Pin Description

|            | Power/Ground Pins  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |  |  |  |

|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Pin Name   | Туре               | Pin No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Description                                                                               |  |  |  |

| VCCIO      | Р                  | 6, 26, 39,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital Power for I/O pins, 3.3V                                                              |  |  |  |

| VCCIO      | Г                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Please add a 0.1uF bypass capacitor between each VCCIO and GND.                               |  |  |  |

| VCCK       | Р                  | 10, 22,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Digital Power for core, 1.2V                                                                  |  |  |  |

| VCCK       | 1                  | 37, 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Please add a 0.1uF bypass capacitor between each VCCK and GND.                                |  |  |  |

| GND        | Р                  | EPAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ground for all Analog and Digital Power.                                                      |  |  |  |

| VCC33A_REG | Р                  | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Analog Power for Regulator, 3.3V                                                              |  |  |  |

|            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.2V Power Output of on-chip 3.3V to 1.2V Regulator.                                          |  |  |  |

| VO12       | Р                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The regulator requires an external capacitor (at least $3.3 \ \mu\text{F}$ ) with low ESR for |  |  |  |

|            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | frequency compensation and stability maintenance.                                             |  |  |  |

| VCC12A_TX  | Р                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Analog Power for PCIe Transmitter, 1.2V.                                                      |  |  |  |

| VCC12A_1A  | 1                  | 37, 57Please add a 0.1uF bypass capacitor between each VCCK and GND.EPADGround for all Analog and Digital Power.36Analog Power for Regulator, 3.3V351.2V Power Output of on-chip 3.3V to 1.2V Regulator.36The regulator requires an external capacitor (at least 3.3 μF) with low 1<br>frequency compensation and stability maintenance.13Analog Power for PCIe Transmitter, 1.2V.<br>Please add a 0.1 and 10 uF bypass capacitor between VCC12A_TX14Analog Power for PCIe Transceiver, 1.2V.<br>Please add a 0.1 and 10 uF bypass capacitor between VCC12A_D and<br>Analog Power for PCIe Auxiliary, 1.2V.18Please add a 0.1 and 10 uF bypass capacitor between VCC12A_AU. | Please add a 0.1 and 10 uF bypass capacitor between VCC12A_TX and GND.                        |  |  |  |

| VCC12A D   | Р                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                               |  |  |  |

| VCC12A_D   | Please add a 0.1 a | Please add a 0.1 and 10 uF bypass capacitor between VCC12A_D and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                               |  |  |  |

|            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |  |  |  |

| VCC12A_AUX | Р                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Please add a 0.1 and 10 uF bypass capacitor between VCC12A_AUX and                            |  |  |  |

|            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND.                                                                                          |  |  |  |

10 Copyright © 2016 ASIX Electronics Corporation. All rights reserved.

## 1.4.1 GPIO and Mode Setting

|                        | GPIO and Mode Setting Pins |                                                                                     |                                                                                                                                                                                                                                                                                                       |  |  |  |

|------------------------|----------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name               | Туре                       | Pin No                                                                              | Pin Description                                                                                                                                                                                                                                                                                       |  |  |  |

| GPIO[23:8]             | B5/CU/4m                   | 31, 32,<br>33, 34,<br>38, 40,<br>41, 42,<br>43, 44,<br>45, 46,<br>47, 48,<br>49, 50 | General Purpose I/O signal<br>GPIO[15:8] are only valid when <b>CHIP_MODE</b> = 100 and 110.<br>GPIO[23:16] are only valid when <b>CHIP_MODE</b> = 100 and 110 and Port 4 was<br>disabled by <b>HWCFGEE</b> . Please reference to Section 3.                                                          |  |  |  |

| GPIO7                  | B5/CU/8m                   | 60                                                                                  | General Purpose Output signal<br>GPIO7 has an optional function is external wakeup pin in input direction. When<br>AX99100 entered to L2 mode, this pin can be used to wakeup AX99100 also.                                                                                                           |  |  |  |

| GPIO6                  | B5/CU/8m                   | 59                                                                                  | General Purpose Output signal<br>GPIO6 has an optional function is a power-down control signal to power down<br>the external transceiver when AX99100 entered to L2 mode. This function can be<br>enabled by setting bit1 and the polarity selection is bit0 in configuration<br>EEPROM, offset 0x55. |  |  |  |

| GPIO5/<br>CHIP_MODE[2] | O5/ 8m                     | 58                                                                                  | General Purpose Output signal when chip exited reset and operating in normal                                                                                                                                                                                                                          |  |  |  |

| GPIO4/<br>CHIP_MODE[1] | O5/8m                      | 56                                                                                  | functional mode.<br>These pins are input direction during chip reset use to bootstrap the mode setting                                                                                                                                                                                                |  |  |  |

| GPIO3/<br>CHIP_MODE[0] | O5/8m                      | 54                                                                                  | to decide the chip operation mode. Please reference to Section 3.1.                                                                                                                                                                                                                                   |  |  |  |

| GPIO2                  | O5/8m                      | 53                                                                                  | General Purpose Output signal when chip exited reset and operating in normal functional mode.<br>This pin should be connected to the AUX 3.3V in PCIe slot via an external pull-up resistor. It is used to detect the 3.3V AUX is existed or not.                                                     |  |  |  |

| GPIO1                  | B5/CU/8m                   | 52                                                                                  | General Purpose I/O signal                                                                                                                                                                                                                                                                            |  |  |  |

| GPIO0                  | B5/CU/8m                   | 51                                                                                  | General Purpose I/O signal                                                                                                                                                                                                                                                                            |  |  |  |

| Table 1-4: GPIO   | and Mode Setting | Pin Description   |

|-------------------|------------------|-------------------|

| 1 auto 1-4. OI 10 | and mode Setting | I III Description |

Note: Above GPIO[7:0] are only valid when **CHIP\_MODE**  $\neq 000$ .

#### **1.4.2** Serial Interface for COM Port

| Table 1-5: Serial Interface | for COM Port Pin Description    |

|-----------------------------|---------------------------------|

| rable 1-5. Serial Interface | 101 COM I OIL I III Description |

| Serial Interface for COM Port |            |        |                                                                                     |  |  |

|-------------------------------|------------|--------|-------------------------------------------------------------------------------------|--|--|

| Pin Name                      | Туре       | Pin No | Pin Description                                                                     |  |  |

| TXD1                          |            | 9      |                                                                                     |  |  |

| TXD2                          | O5/4m      | 68     | Transmit data output to transceiver or IrDA data output to IR LED                   |  |  |

| TXD3                          | 03/411     | 50     | Transmit data output to transcerver of TDA data output to TK LED                    |  |  |

| TXD4                          |            | 42     |                                                                                     |  |  |

|                               |            |        | Data Terminal Ready                                                                 |  |  |

| DTR1                          |            | 8      | These pins have internal pull-down during reset. If there is the external pull-up   |  |  |

| DTR2                          | B5/PD/4m   | 67     | resisters connected to these pins separately, it will work for RS-232 function with |  |  |

| DTR3                          | DJ/TD/4III | 49     | active low. Otherwise, it will work for RS-485 function (DXEN) with active high     |  |  |

| DTR4                          |            | 41     | and the output can be enabled by register (the default is disabled). Please         |  |  |

|                               |            |        | reference to Section 3.2.                                                           |  |  |

| RTS1                          |            | 7      | Request to send (Active Low)                                                        |  |  |

| RTS2                          | O5/4m      | 66     |                                                                                     |  |  |

| RTS3                          | 03/411     | 48     | Note: These pins will be changed to RXEN when Software enabled RS-485               |  |  |

| RTS4                          |            | 40     | function for the corresponding ports.                                               |  |  |

| RXD1                          |            | 5      |                                                                                     |  |  |

| RXD2                          | I5/PU      | 65     | Serial received data input from transceiver or IrDA data input from IrDA            |  |  |

| RXD3                          | 13/FU      | 47     | detector.                                                                           |  |  |

| RXD4                          |            | 38     |                                                                                     |  |  |

| RI1                           |            | 3      |                                                                                     |  |  |

| RI2                           | 15         | 64     | Ring Indicator (Active Low)                                                         |  |  |

| RI3                           | 15         | 46     | King indicator (Active Low)                                                         |  |  |

| RI4                           |            | 34     |                                                                                     |  |  |

| DSR1                          |            | 4      |                                                                                     |  |  |

| DSR2                          | 15         | 63     | Data Set Ready (Active Low)                                                         |  |  |

| DSR3                          | 15         | 45     | Data Set Ready (Active Low)                                                         |  |  |

| DSR4                          |            | 33     |                                                                                     |  |  |

| DCD1                          |            | 2      |                                                                                     |  |  |

| DCD2                          | 15         | 62     | Data Comion Datast (Astiva Low)                                                     |  |  |

| DCD3                          | 13         | 44     | Data Carrier Detect (Active Low)                                                    |  |  |

| DCD4                          |            | 32     |                                                                                     |  |  |

| CTS1                          |            | 1      |                                                                                     |  |  |

| CTS2                          | 15         | 61     | Clear to send (Active Low)                                                          |  |  |

| CTS3                          | 15         | 43     |                                                                                     |  |  |

| CTS4                          |            | 31     |                                                                                     |  |  |

Note 1: Serial Port 1 and 2 are only valid when **CHIP\_MODE** = 001, 011, 101 and 110.

Note 2: Serial Port 3 and 4 are only valid when  $CHIP\_MODE = 011$ .

#### 1.4.3 Serial Interface for Multi-Protocol Transceiver

Table 1-6: Serial Interface for Multi-Protocol Transceiver Pin Description

| Serial interface for Multi-Protocol Transceiver              |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name         Type         Pin No         Pin Description |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| O5/4m                                                        | 9<br>68<br>50<br>42                                | Transmit data output to transceiver or IrDA data output to IR LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| B5/PD/4m                                                     | 8<br>67<br>49<br>41                                | Driver Enable<br>These pins have internal pull-down during reset. If there is the external pull-up<br>resisters connected to these pins separately, it will work for RS-232 function with<br>active low. Otherwise, it will work for RS-485 function with active high and the<br>output can be enabled by register (the default is disabled). Please reference to<br>Section3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| O5/4m                                                        | 7<br>66<br>48<br>40                                | Request to send (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| O5/PU/4m                                                     | 5<br>65<br>47<br>38                                | Serial received data input from transceiver or IrDA data input from IrDA detector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| O5/4m                                                        | 3<br>64<br>46<br>34                                | Interface Selection<br>1: RS-485 selected<br>0: RS-232 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| O5/4m                                                        | 4<br>63<br>45<br>33                                | RS485 Termination Enable for transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| O5/4m                                                        | 2<br>62<br>44<br>32                                | Receiver Enable<br>1: Enable Receiver<br>0: Disable Receiver<br>Note: Software should enable RS-485 function for the corresponding ports first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 15                                                           | 1<br>61<br>43<br>31                                | Clear to send (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                                              | O5/4m<br>B5/PD/4m<br>O5/4m<br>O5/4m<br>O5/4m<br>I5 | $\begin{array}{c c c c c c } \hline \textbf{Type} & \textbf{Pin No} \\ \hline \textbf{Pin No} \\ \hline 9 \\ 68 \\ 50 \\ 42 \\ \hline \textbf{B5/PD/4m} & \begin{array}{c} 8 \\ 67 \\ 49 \\ 41 \\ \hline 0 \\ 5 \\ 05/4m \\ \hline 0 \\ 66 \\ 48 \\ 40 \\ \hline 0 \\ 5 \\ 05/4m \\ \hline 1 \\ 65 \\ 47 \\ 38 \\ \hline 0 \\ 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 40 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 41 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 41 \\ \hline 5 \\ 65 \\ 47 \\ 38 \\ \hline 41 \\ 65 \\ 33 \\ \hline 5 \\ 05/4m \\ \hline 1 \\ 61 \\ 43 \\ \hline 15 \\ \hline 1 \\ 61 \\ 43 \\ \hline \end{array}$ |  |  |  |  |

Note 1: Serial Port 1 and 2 are only valid when  $CHIP\_MODE = 010, 100 \text{ and } 111$ .

Note 2: Serial Port 3 and 4 are only valid when **CHIP\_MODE** = 101 and 111.

#### 1.4.4 Serial Port with GPIO enabled

#### Table 1-7: Serial Interface for GPIO Enabled Pin Description

| Enable Serial Port for GPIO mode |                                                                                   |    |                                                                                    |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------|--|--|--|

| Pin Name                         | Type   Pin No   Pin Description                                                   |    |                                                                                    |  |  |  |

| TXD1                             |                                                                                   | 9  |                                                                                    |  |  |  |

| TXD2                             | 68                                                                                |    | Transmit data output to transposition on LaDA data output to ID LED                |  |  |  |

| TXD3                             | O5/4m                                                                             | 50 | Transmit data output to transceiver or IrDA data output to IR LED                  |  |  |  |

| TXD4                             |                                                                                   | 42 |                                                                                    |  |  |  |

| SP1_GPIO0                        |                                                                                   | 8  |                                                                                    |  |  |  |

| SP2_GPIO0                        | B5/CU/4m                                                                          | 67 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO0                        | DJ/CU/4III                                                                        | 49 |                                                                                    |  |  |  |

| SP4_GPIO0                        |                                                                                   | 41 |                                                                                    |  |  |  |

| SP1_GPIO1                        |                                                                                   | 7  |                                                                                    |  |  |  |

| SP2_GPIO1                        | B5/CU/4m                                                                          | 66 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO1                        | DJ/CU/4III                                                                        | 48 |                                                                                    |  |  |  |

| SP4_GPIO1                        |                                                                                   | 40 |                                                                                    |  |  |  |

| RXD1                             |                                                                                   | 5  |                                                                                    |  |  |  |

| RXD2                             | O5/PU/4m                                                                          | 65 | Serial receives data input from transceiver or IrDA data input from IrDA detector. |  |  |  |

| RXD3                             | 03/F0/411                                                                         | 47 | Serial receives data input from transcerver of frDA data input from frDA detector. |  |  |  |

| RXD4                             |                                                                                   | 38 |                                                                                    |  |  |  |

| SP1_GPIO5                        |                                                                                   | 3  |                                                                                    |  |  |  |

| SP2_GPIO5                        | B5/CU/4m                                                                          | 64 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO5                        | DJ/CU/4III                                                                        | 46 |                                                                                    |  |  |  |

| SP4_GPIO5                        |                                                                                   | 34 |                                                                                    |  |  |  |

| SP1_GPIO3                        |                                                                                   | 4  |                                                                                    |  |  |  |

| SP2_GPIO3                        | B5/CU/4m                                                                          | 63 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO3                        | DJ/CU/4III                                                                        | 45 |                                                                                    |  |  |  |

| SP4_GPIO3                        |                                                                                   | 33 |                                                                                    |  |  |  |

| SP1_GPIO4                        |                                                                                   | 2  |                                                                                    |  |  |  |

| SP2_GPIO4                        | B5/CU/4m                                                                          | 62 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO4                        | D3/CU/4III                                                                        | 44 |                                                                                    |  |  |  |

| SP4_GPIO4                        |                                                                                   | 32 |                                                                                    |  |  |  |

| SP1_GPIO2                        |                                                                                   | 1  |                                                                                    |  |  |  |

| SP2_GPIO2                        | B5/CU/4m                                                                          | 61 | Serial Port GPIO                                                                   |  |  |  |

| SP3_GPIO2                        | DJ/CU/4III                                                                        | 43 |                                                                                    |  |  |  |

| SP4_GPIO2                        |                                                                                   | 31 |                                                                                    |  |  |  |

| NT. ( A 1                        | $1 \cdot 1 \cdot$ |    | on are valid when Software enabled the CDIO function by register setting in each   |  |  |  |

Note: Above Serial Port GPIO function are valid when Software enabled the GPIO function by register setting in each functions.

#### 1.4.5 Serial Port with Function Disabled

Table 1-8: Serial Interface with Port2 and Port4 Disabled Pin Description

|           | Serial Interface with Port2 and Port4 Disabled |        |                                                                   |  |  |  |

|-----------|------------------------------------------------|--------|-------------------------------------------------------------------|--|--|--|

| Pin Name  | Туре                                           | Pin No | Pin Description                                                   |  |  |  |

| TXD2      | O5/4m                                          | 68     | No any function for this pin due to disable.                      |  |  |  |

| TXD4      |                                                | 42     |                                                                   |  |  |  |

| SP1_GPIO0 | B5/CU/4m                                       | 67     | Serial Port GPIO <sup>(Note 2)</sup>                              |  |  |  |

| SP3_GPIO0 |                                                | 41     |                                                                   |  |  |  |

| SP1_GPIO1 | B5/CU/4m                                       | 66     | Serial Port GPIO                                                  |  |  |  |

| SP3_GPIO1 |                                                | 40     |                                                                   |  |  |  |

| RXD2      | O5/PU/4m                                       | 65     | No any function for this pin due to disable.                      |  |  |  |

| RXD4      |                                                | 38     |                                                                   |  |  |  |

| SP1_GPIO5 | B5/CU/4m                                       | 64     | Serial Port GPIO                                                  |  |  |  |

| SP3_GPIO5 |                                                | 34     |                                                                   |  |  |  |

| SP1_GPIO3 | B5/CU/4m                                       | 63     | Serial Port GPIO                                                  |  |  |  |

| SP3_GPIO3 |                                                | 33     |                                                                   |  |  |  |

| SP1_GPIO4 | B5/CU/4m                                       | 62     | Serial Port GPIO                                                  |  |  |  |

| SP3_GPIO4 |                                                | 32     |                                                                   |  |  |  |

| SP1_GPIO2 | B5/CU/4m                                       | 61     | Serial Port GPIO                                                  |  |  |  |

| SP3_GPIO2 |                                                | 31     | d by softing HWCECEE when CHID MODE softing for these sorial port |  |  |  |

Note 1: If Port 2 or Port 4 are disabled by setting **HWCFGEE** when **CHIP\_MODE** setting for those serial port interface, all pins for Port 2 or Port 4 (excluded TXD and RXD) will be re-directed to the GPIO function of Port 1 and Port 3. Thus the pins of Port 1 and Port 3 cannot be set for GPIO function by software register setting.

Note 2: Pin 67 and 41 will be re-directed to DTR1/DXEN1 and DTR3/DXEN3 also. However software can enable it to GPIO function as SP1\_GPIO0 and SP3\_GPIO0.

#### 1.4.6 Parallel Port

| Parallel Port Interface |                                     |                                         |                                                                                                                                                                                                                                                |  |  |  |

|-------------------------|-------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                | Туре                                | Pin No                                  | Pin Description                                                                                                                                                                                                                                |  |  |  |

| STROBEn                 | SPP:<br>O5/T/4m<br>Others:<br>O5/4m | 42                                      | Set active low by the host to transfer data into the input latch of the peripheral.<br>Data are valid while STROBEn is low.<br>The pin is open-drain when operation in SPP mode, otherwise, is direct drive<br>logic 0 or logic 1.             |  |  |  |

| AUTOLFn                 | SPP:<br>O5/T/4m<br>Others:<br>O5/4m | 41                                      | The interpretation of this signal varies from peripheral to peripheral. Set low by host to put some printers into auto-line feed mode<br>The pin is open-drain when operation in SPP mode, otherwise, is direct drive logic 0 or logic 1.      |  |  |  |

| INITn                   | SPP:<br>O5/T/4m<br>Others:<br>O5/4m | 40                                      | Pulsed low by the host in conjunction with IEEE 1284 Active low to reset the interface and force a return to Compatibility Mode idle phase<br>The pin is open-drain when operation in SPP mode, otherwise, is direct drive logic 0 or logic 1. |  |  |  |