# Preliminary 512K X 32 Bit X 4 Banks Low Power Synchronous DRAM

# **Document Title**

# 512K X 32 Bit X 4 Banks Low Power Synchronous DRAM

# **Revision History**

| Rev. No. | <u>History</u>            | Issue Date        | <u>Remark</u> |

|----------|---------------------------|-------------------|---------------|

| 0.0      | Initial issue             | March 21, 2007    | Preliminary   |

| 0.1      | Add part numbering scheme | February 19, 2008 |               |

# A43E16321

# Preliminary

# 512K X 32 Bit X 4 Banks Low Power Synchronous DRAM

#### Features

- Low power supply

- VDD: 1.8V VDDQ : 1.8V

- LVCMOS compatible with multiplexed address

- Four banks / Pulse RAS

- MRS cycle with address key programs

- CAS Latency (2 & 3)

- Burst Length (1,2,4,8 & full page)

- Burst Type (Sequential & Interleave)

- All inputs are sampled at the positive going edge of the system clock

- Deep Power Down Mode

- DQM for masking

- Auto & self refresh

- Clock Frequency (max) : 105MHz @ CL=3 (-95) 133MHz @ CL=3 (-75)

- 64ms refresh period (4K cycle)

- Self refresh with programmable refresh period through EMRS cycle

- Programmable Power Reduction Feature by partial array activation during Self-refresh through EMRS cycle

- Auto TCSR

- Industrial operating temperature range: -40°C to +85°C for -U series

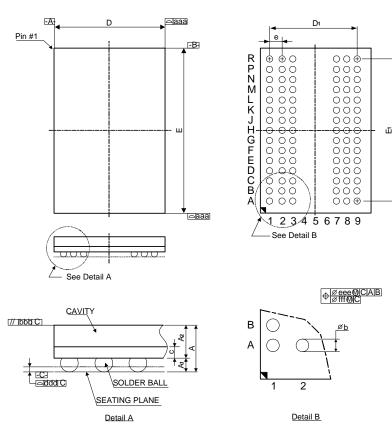

- Available in 90 Balls CSP (8mm X 13mm)

- Package is available to lead free (-F series)

- All Pb-free (Lead-free) products are RoHS compliant

#### **General Description**

The A43E16321 is 67,108,864 bits Low Power synchronous high data rate Dynamic RAM organized as 2 X 1,048,576 words by 32 bits, fabricated with AMIC's high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock.

#### Pin Configuration

#### ■ 90 Balls CSP (8 mm x 13 mm)

**Top View**

I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable latencies allows the same device to be useful for a variety of high bandwidth, high performance memory system applications.

|   | 90 Ball (8X13) CSP |      |      |       |             |      |  |  |  |  |  |  |

|---|--------------------|------|------|-------|-------------|------|--|--|--|--|--|--|

|   | 1                  | 2    | 3    | 3 7 8 |             | 9    |  |  |  |  |  |  |

| А | DQ26               | DQ24 | VSS  | VDD   | DQ23        | DQ21 |  |  |  |  |  |  |

| В | DQ28               | VDDQ | VSSQ | VDDQ  | VSSQ        | DQ19 |  |  |  |  |  |  |

| С | VSSQ               | DQ27 | DQ25 | DQ22  | DQ20        | VDDQ |  |  |  |  |  |  |

| D | VSSQ               | DQ29 | DQ30 | DQ17  | DQ18        | VDDQ |  |  |  |  |  |  |

| E | VDDQ               | DQ31 | NC   | NC    | DQ16        | VSSQ |  |  |  |  |  |  |

| F | VSS                | DQM3 | A3   | A2    | DQM2        | VDD  |  |  |  |  |  |  |

| G | A4                 | A5   | A6   | A10   | A0          | A1   |  |  |  |  |  |  |

| Н | A7                 | A8   | NC   | NC    | BA1         | NC   |  |  |  |  |  |  |

| J | CLK                | CKE  | A9   | BA0   | CS          | RAS  |  |  |  |  |  |  |

| К | DQM1               | NC   | NC   | CAS   | WE          | DQMo |  |  |  |  |  |  |

| L | VDDQ               | DQ8  | VSS  | VDD   | DQ7         | VSSQ |  |  |  |  |  |  |

| М | VSSQ               | DQ10 | DQ9  | DQ6   | DQ5         | VDDQ |  |  |  |  |  |  |

| Ν | VSSQ               | DQ12 | DQ14 | DQ1   | DQ3         | VDDQ |  |  |  |  |  |  |

| Р | DQ11               | VDDQ | VSSQ | VDDQ  | VSSQ        | DQ4  |  |  |  |  |  |  |

| R | DQ13               | DQ15 | VSS  | VDD   | DQ <b>o</b> | DQ2  |  |  |  |  |  |  |

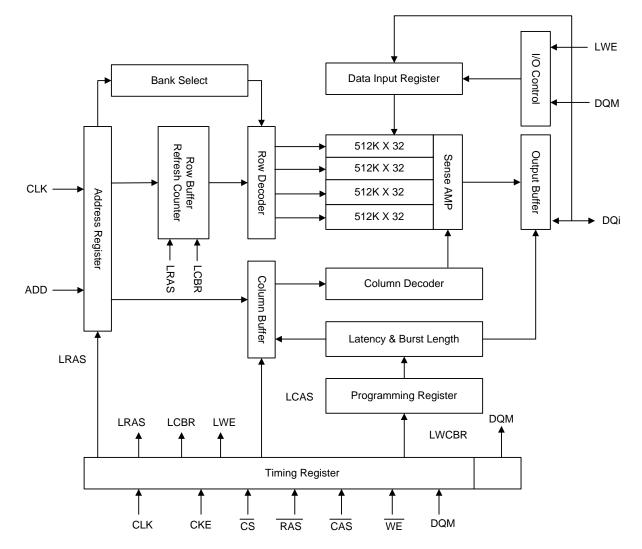

#### **Block Diagram**

# **Pin Descriptions**

| Symbol    | Name                        | Description                                                                                    |  |  |  |  |  |

|-----------|-----------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CLK       | System Clock                | Active on the positive going edge to sample all inputs.                                        |  |  |  |  |  |

| cs        | Chip Select                 | Disables or Enables device operation by masking or enabling all inputs except CLK, CKE and DQM |  |  |  |  |  |

|           |                             | Masks system clock to freeze operation from the next clock cycle.                              |  |  |  |  |  |

| CKE       | Clock Enable                | CKE should be enabled at least one clock + tss prior to new command.                           |  |  |  |  |  |

|           |                             | Disable input buffers for power down in standby.                                               |  |  |  |  |  |

| A0~A10    | Address                     | Row / Column addresses are multiplexed on the same pins.                                       |  |  |  |  |  |

| A0~A10    | Address                     | Row address : RA0~RA10, Column address: CA0~CA7                                                |  |  |  |  |  |

| BA0, BA1  | Bank Select Address         | Selects bank to be activated during row address latch time.                                    |  |  |  |  |  |

| DAU, DAT  | Bark Select Address         | Selects band for read/write during column address latch time.                                  |  |  |  |  |  |

|           | Row Address Strobe          | Latches row addresses on the positive going edge of the CLK with $\overline{RAS}$ low.         |  |  |  |  |  |

| RAS       | Row Address Strobe          | Enables row access & precharge.                                                                |  |  |  |  |  |

|           | Column Address              | Latches column addresses on the positive going edge of the CLK with CAS low.                   |  |  |  |  |  |

| CAS       | Strobe                      | Enables column access.                                                                         |  |  |  |  |  |

| WE        | Write Enable                | Enables write operation and Row precharge.                                                     |  |  |  |  |  |

| DQMi      | Data Input/Output           | Makes data output Hi-Z, t SHZ after the clock and masks the output.                            |  |  |  |  |  |

| DQIVII    | Mask                        | Blocks data input when DQM active.                                                             |  |  |  |  |  |

| DQ0-31    | Data Input/Output           | Data inputs/outputs are multiplexed on the same pins.                                          |  |  |  |  |  |

| VDD/VSS   | Power<br>Supply/Ground      | Power Supply: +1.7V ~ 1.95V/Ground                                                             |  |  |  |  |  |

| VDDQ/VSSQ | Data Output<br>Power/Ground | Provide isolated Power/Ground to DQs for improved noise immunity.                              |  |  |  |  |  |

| NC/RFU    | No Connection               |                                                                                                |  |  |  |  |  |

MIC

#### **Absolute Maximum Ratings\***

| Voltage on any pin relative to VSS (Vin, Vout)    |

|---------------------------------------------------|

|                                                   |

| Voltage on VDD supply relative to VSS (VDD, VDDQ) |

|                                                   |

| Storage Temperature (Tstg)55°C to +150°C          |

| Soldering Temperature X Time (TsLoder)            |

|                                                   |

| Power Dissipation (Pb) 0.8W                       |

| Short Circuit Current (los) 50mA                  |

#### \*Comments

Permanent device damage may occur if "Absolute Maximum Ratings" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

#### Capacitance (TA=25°C, f=1MHz)

| Parameter                     | Symbol | Condition                                                                               | Min | Max | Unit |

|-------------------------------|--------|-----------------------------------------------------------------------------------------|-----|-----|------|

| Input Capacitance             | CI1    | A0 to A10, BA0, BA1                                                                     | 2.0 | 4.0 | pF   |

|                               | CI2    | CLK, CKE, $\overline{CS}$ , $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ , DQM | 2.0 | 4.0 | pF   |

| Data Input/Output Capacitance | CI/O   | DQo to DQ31                                                                             | 3.5 | 6.0 | pF   |

#### **DC Electrical Characteristics**

Recommend operating conditions (Voltage referenced to VSS = 0V,  $T_A = 0^{\circ}C$  to +70°C or  $T_A = -40^{\circ}C$  to +85°C)

| Parameter                                    | Symbol | Min        | Тур | Мах      | Unit | Note         |

|----------------------------------------------|--------|------------|-----|----------|------|--------------|

| Supply Voltage                               | VDD    | 1.7        | 1.8 | 1.95     | V    |              |

| DQ Supply Voltage                            | VDDQ   | 1.7        | 1.8 | 1.95     | V    |              |

| Input High Voltage                           | Viн    | 0.8*VDDQ   | -   | VDDQ+0.3 | V    |              |

| Input Low Voltage                            | Vil    | -0.3       | -   | 0.3      | V    | Note 1       |

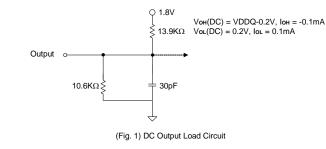

| Output High Voltage                          | Vон    | VDDQ - 0.2 | -   | -        | V    | Іон = -0.1mA |

| Output Low Voltage                           | Vol    | -          | -   | 0.2      | V    | lo∟ = 0.1mA  |

| Input Leakage Current                        | lı∟    | -1         | -   | 1        | μA   | Note 2       |

| Output Leakage Current                       | lo∟    | -1.5       | -   | 1.5      | μA   | Note 3       |

| Output Loading Condition See Fig. 1 (Page 6) |        |            |     |          |      | •            |

Note: 1. VIL (min) = -1.5V AC (pulse width  $\leq$  5ns).

2. Any input  $0V \le VIN \le VDD + 0.3V$ , all other pins are not under test = 0V

3. Dout is disabled,  $0V \le Vout \le VDD$

#### **Decoupling Capacitance Guide Line**

Recommended decoupling capacitance added to power line at board

| Parameter                                    | Symbol | Value      | Unit |

|----------------------------------------------|--------|------------|------|

| Decoupling Capacitance between VDD and VSS   | Cdc1   | 0.1 + 0.01 | μF   |

| Decoupling Capacitance between VDDQ and VSSQ | Cdc2   | 0.1 + 0.01 | μF   |

Note: 1. VDD and VDDQ pins are separated each other.

All VDD pins are connected in chip. All VDDQ pins are connected in chip.

All VSS pins are connected in chip. All VSSQ pins are connected in chip.

#### **DC Electrical Characteristics**

Recommend operating conditions (Voltage referenced to VSS = 0V,  $T_A = 0^{\circ}C$  to +70°C or  $T_A = -40^{\circ}C$  to +85°C)

| Symbol | vmbol Parameter Test Conditions                                                                                                                      |                                                                                                    |         |     |     | Units | Note |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------|-----|-----|-------|------|

| 0,     |                                                                                                                                                      |                                                                                                    |         | -75 | -95 |       |      |

| lcc1   | Operating Current<br>(One Bank Active)                                                                                                               | Burst Length = 1<br>trc $\geq$ trc(min), tcc $\geq$ tcc(min), loL = 0m.                            | A       | 6   | 0   | mA    | 1    |

| Icc2 P | Precharge Standby Current in power-down mode                                                                                                         | $CKE \le VIL(max)$ , tcc = 10ns                                                                    | 0       | .4  | mA  |       |      |

| lcc2N  | Precharge Standby Current<br>in non power-down mode                                                                                                  | CKE $\ge$ VIH(min), $\overrightarrow{CS} \ge$ VIH(min), tcc = Input signals are changed one time d | :       | 3   | mA  |       |      |

| lcc3P  | Active Standby current in                                                                                                                            | CKE ≤ Vi∟(max), tcc = 10ns                                                                         | :       | 3   |     |       |      |

| Icc3N  | non power-down mode<br>(One Bank Active) $$<br>CKE $\geq$ VIH(min), CS $\geq$ VIH(min), tcc = 10ns<br>Input signals are changed one time during 20ns |                                                                                                    |         |     |     | mA    |      |

| lcc4   | Operating Current<br>(Burst Mode)                                                                                                                    | IoL = 0mA, Page Burst, CAS Latency<br>All bank Activated, tccp = tccp (min), t                     |         | 6   | 5   | mA    | 1    |

| lcc5   | Refresh Current                                                                                                                                      | tск = 10ns                                                                                         |         | 10  | 00  | mA    | 2    |

|        |                                                                                                                                                      |                                                                                                    | 4 Banks | 30  | 00  |       |      |

| Icc6   | Self Refresh Current                                                                                                                                 | $CKE \leq 0.2V$                                                                                    | 2 Banks | 240 |     | uA    |      |

|        |                                                                                                                                                      |                                                                                                    | 1 Banks | 20  | 00  |       |      |

| lcc7   | Deep Power Down Current                                                                                                                              | $CKE \le 0.2V$                                                                                     |         | 1   | 0   | uA    |      |

Note: 1. Measured with outputs open. Addresses are changed only one time during tcc(min).

2. Refresh period is 64ms. Addresses are changed only one time during tcc(min).

<sup>2.</sup> VSS and VSSQ pins are separated each other

# **AC Operating Test Conditions**

(VDD = 3.3V  $\pm$ 0.3V, Ta = 0°C to +70°C or Ta = -40°C to +85°C)

| Parameter                                 | Value          | Unit |

|-------------------------------------------|----------------|------|

| AC input levels                           | 0.9 x VDDQ/0.2 | V    |

| Input timing measurement reference level  | 0.5 x VDDQ     | V    |

| Input rise and all time (See note3)       | tr/tf = 1/1    | ns   |

| Output timing measurement reference level | 0.5 x VDDQ     | V    |

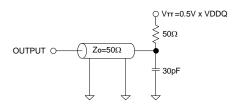

| Output load condition                     | See Fig.2      |      |

(Fig. 2) AC Output Load Circuit

#### **AC Characteristics**

(AC operating conditions unless otherwise noted)

| Symbol | Paramete                             | -7             | 75  | -9   | 5   | Unit | Note |     |

|--------|--------------------------------------|----------------|-----|------|-----|------|------|-----|

| Symbol | Faiamen                              | Min            | Max | Min  | Max | Unit | Note |     |

| tcc    | CLK avela time                       | CAS Latency =3 | 7.5 | 1000 | 9.5 | 1000 |      |     |

| icc    | CLK cycle time                       | CAS Latency =2 | 12  | 1000 | 15  | 1000 | ns   | 1   |

| tava   | tsac CLK to valid output delay       | CAS Latency =3 | -   | 6    | -   | 7    | 20   | 1,2 |

| tsac   |                                      | CAS Latency =2 | -   | 8    | -   | 9    | ns   | ∟,۲ |

| toн    | Output data hold time                | 2              | -   | 2    | -   | ns   | 2    |     |

| tсн    | CLK bigh pulse width                 | CAS Latency =3 | 2.5 | -    | 3   | -    | ns   | 3   |

| ICH    | CLK high pulse width                 | CAS Latency =2 | 2.5 | -    | 3   | -    |      | 3   |

| tcL    | CLK low pulse width                  | CAS Latency =3 | 2.5 | -    | 3   | -    | 20   | 3   |

| ICL    |                                      | CAS Latency =2 | 2.5 | -    | 3   | -    | ns   | 3   |

| taa    | Innut actus time                     | CAS Latency =3 | 2   | -    | 2   | -    | 20   | 3   |

| tss    | Input setup time                     | CAS Latency =2 | 2   | -    | 2   | -    | ns   | 3   |

| tsн    | Input hold time                      | 1              | -   | 1    | -   | ns   | 3    |     |

| ts∟z   | CLK to output in Low-Z               |                | 1   | -    | 1   | -    | ns   | 2   |

| touz   | CLK to output in Hi 7                | CAS Latency =3 | -   | 6    | -   | 7    | 200  |     |

| tsнz   | CLK to output in Hi-Z CAS Latency =2 |                | -   | 8    | -   | 8    | ns   |     |

CL=CAS Latency.

\*All AC parameters are measured from half to half.

Note : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

# **Operating AC Parameter**

(AC operating conditions unless otherwise noted)

| Symbol    | Parameter                           | Vers | ion | Unit | Note |

|-----------|-------------------------------------|------|-----|------|------|

| Symbol    | Farameter                           | -75  | -95 | Onit | Note |

| trrd(min) | Row active to row active delay      | 15   | 19  | ns   | 1    |

| trcd(min) | RAS to CAS delay                    | 20   | 24  | ns   | 1    |

| tRP(min)  | Row precharge time                  | 20   | 24  | ns   | 1    |

| tRAS(min) | Row active time                     | 50   | 50  | ns   | 1    |

| tRAS(max) |                                     | 100  | 100 | μS   |      |

| tRC(min)  | Row cycle time                      | 72.5 | 74  | ns   | 1    |

| tcDL(min) | Last data in new col. Address delay | 7.5  | 9.5 | ns   | 2    |

| tRDL(min) | Last data in row precharge          | 15   | 15  | ns   | 2    |

| tBDL(min) | Last data in to burst stop          | 7.5  | 9.5 | ns   | 2    |

| tccD(min) | Col. Address to col. Address delay  | 7.5  | 9.5 | ns   |      |

Note: 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.2. Minimum delay is required to complete write.

#### **Simplified Truth Table**

|                           | Command                    |         | CKEn-1 | CKEn | CS     | RAS    | CAS    | WE     | DQM | BA0,<br>BA1 | A10<br>/AP | A9~A0           | Notes    |

|---------------------------|----------------------------|---------|--------|------|--------|--------|--------|--------|-----|-------------|------------|-----------------|----------|

| Register                  | Mode Regis                 | ter Set | н      | х    | L      | L      | L      | L      | x   | OP CODE     |            | ODE             | 1,2      |

| Extended Mod              | e Register Se              | ət      | Н      | Х    | L      | L      | L      | L      | L   |             | OP C       | ODE             | 1,2      |

| Refresh                   | Auto Refres                | h       |        | Н    |        | _      | _      |        |     |             |            |                 | 3        |

|                           | Self                       | Entry   | Н      | L    | L      | L      | L      | Н      | Х   |             | Х          |                 | 3        |

|                           | Refresh                    | Exit    | L      | н    | L      | Н      | Н      | Н      | x   |             | х          | ,               | 3        |

|                           |                            | LAR     |        |      | Н      | Х      | Х      | Х      | ~   |             |            |                 | 3        |

| Bank Active &             | Row Addr.                  |         | Н      | Х    | L      | L      | Н      | Н      | Х   | V           | Ro         | w Addr.         | 4        |

| Read &<br>Column Addr.    | Auto Precha<br>Auto Precha |         | н      | х    | L      | н      | L      | н      | x   | v           | L<br>H     | Column<br>Addr. | 4<br>4,5 |

| Write &<br>Column Addr.   | Auto Precharge Disable     |         | н      | x    | L      | н      | L      | L      | x   | v           | L          | Column<br>Addr. | 4        |

| Burst Stop                |                            | •       | Н      | Х    | L      | Н      | Н      | L      | Х   |             | Х          | (               | 6        |

| Precharge                 | Bank Select                | ion     | н      | x    | L      | L      | н      | L      | x   | V           | L          | х               |          |

|                           | Both Banks                 |         |        |      |        |        |        |        |     | Х           | Н          |                 |          |

| Clock Suspend             | d or                       | Entry   | н      | L    | L<br>H | H      | H      | H<br>X | х   |             |            |                 |          |

| Active Power I            | Down                       | Exit    | L      | н    | Х      | X<br>X | X<br>X | X      | x   |             | Х          | (               |          |

|                           |                            |         |        |      | L      | H      | H      | H      | ~   |             |            |                 |          |

|                           |                            | Entry   | Н      | L    | H      | X      | X      | X      | X   |             |            |                 |          |

| Precharge Power Down Mode |                            | L       | н      | L    | V<br>X | V<br>X | V<br>X | x      | X   |             |            |                 |          |

| DQM                       |                            | Н       |        |      | X      | ~      |        | V      |     | Х           | (          | 7               |          |

|                           |                            |         |        | v    | L      | Н      | Н      | Н      | V   |             |            |                 |          |

| No Operation              | No Operation Command       |         | Н      | Х    | Н      | Х      | Х      | Х      | Х   |             | Х          |                 |          |

| Deep Power D              | own Entry                  |         | Н      | L    | L      | Н      | Н      | L      | Х   |             | Х          |                 |          |

| Deep Power D              | own Exit                   |         | L      | Н    | Х      | Х      | Х      | Х      | Х   |             | Х          | (               | 8        |

(V = Valid, X = Don't Care, H = Logic High, L = Logic Low)

Note: 1. OP Code: Operand Code

A0~A10, BA0, BA1: Program keys. (@MRS, EMRS) 2. MRS can be issued only when all banks are at precharge state.

A new command can be issued after 2 clock cycle of MRS, EMRS.

3. Auto refresh functions is same as CBR refresh of DRAM. The automatical precharge without Row precharge command is meant by "Auto". Auto/Self refresh can be issued only when all banks are at precharge state.

4. BA : Bank select address.

5. During burst read or write with auto precharge, new read/write command cannot be issued. Another bank read/write command can be issued at every burst length.

6. Bust stop command is valid at every burst length.

DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0) but masks the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2)

8. After Deep Power Down mode exit, a full new initialization of the memory device is mandatory.

#### Mode Register Filed Table to Program Modes

Register Programmed with MRS

| Address  | BA1  | BA0  | A10      | A9     | A8   | A7 | A6 | A5       | A4 | A3 | A2 | A1        | A0  |

|----------|------|------|----------|--------|------|----|----|----------|----|----|----|-----------|-----|

| Function | 0    | 0    | RFU      | W.B.L  | Т    | М  | CA | AS Laten | су | BT | Βι | urst Leng | ith |

|          | (Not | e 3) | (Note 1) | ) (Not | e 2) |    |    |          |    |    |    |           |     |

|            |              | Test Mode         | CAS Latency |    |    |          | В  | urst Type  | Burst Length |    |    |           |          |  |

|------------|--------------|-------------------|-------------|----|----|----------|----|------------|--------------|----|----|-----------|----------|--|

| <b>A</b> 8 | A7           | Туре              | A6          | A5 | A4 | Latency  | A3 | A3 Type    |              | A1 | A0 | BT=0      | BT=1     |  |

| 0          | 0            | Mode Register Set | 0           | 0  | 0  | Reserved | 0  | Sequential | 0            | 0  | 0  | 1         | 1        |  |

| 0          | 1            | Vendor            | 0           | 0  | 1  | -        | 1  | Interleave | 0            | 0  | 1  | 2         | 2        |  |

| 1          | 0            | Use               | 0           | 1  | 0  | 2        |    |            | 0            | 1  | 0  | 4         | 4        |  |

| 1          | 1            | Only              | 0           | 1  | 1  | 3        |    |            | 0            | 1  | 1  | 8         | 8        |  |

|            | Writ         | te Burst Length   | 1           | 0  | 0  | Reserved |    |            | 1            | 0  | 0  | Reserved  | Reserved |  |

| A9         |              | Length            | 1           | 0  | 1  | Reserved |    |            | 1            | 0  | 1  | Reserved  | Reserved |  |

| 0          | 0 Burst      |                   | 1           | 1  | 0  | Reserved | 1  |            | 1            | 1  | 0  | Reserved  | Reserved |  |

| 1          | 1 Single Bit |                   | 1           | 1  | 1  | Reserved | 1  |            | 1            | 1  | 1  | 256(Full) | Reserved |  |

Note: 1. RFU(Reserved for Future Use) should stay "0" during MRS cycle.

2. If A9 is high during MRS cycle, "Burst Read Single Bit Write" function will be enabled.

3. BA1=0, BA0=0 select the Mode Register (vs. the Extended Mode Register).

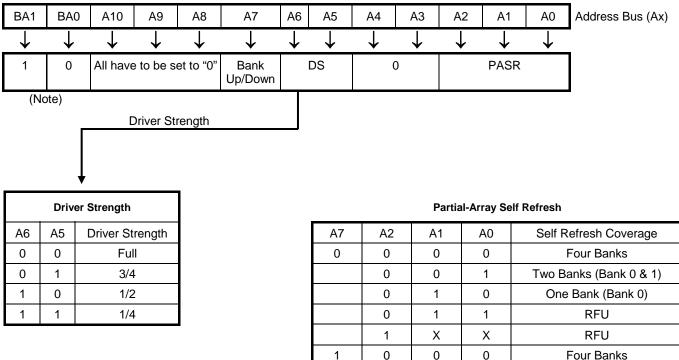

#### **Extended Mode Register Table**

| A7 | A2 | A1 | A0 | Self Refresh Coverage  |

|----|----|----|----|------------------------|

| 0  | 0  | 0  | 0  | Four Banks             |

|    | 0  | 0  | 1  | Two Banks (Bank 0 & 1) |

|    | 0  | 1  | 0  | One Bank (Bank 0)      |

|    | 0  | 1  | 1  | RFU                    |

|    | 1  | Х  | Х  | RFU                    |

| 1  | 0  | 0  | 0  | Four Banks             |

|    | 0  | 0  | 1  | Two Banks (Bank 2 & 3) |

|    | 0  | 1  | 0  | One Bank (Bank 2)      |

|    | 0  | 1  | 1  | RFU                    |

|    | 1  | Х  | Х  | RFU                    |

Note: BA1=1, BA0=0 select the Extended Mode Register (vs. the Mode Register)

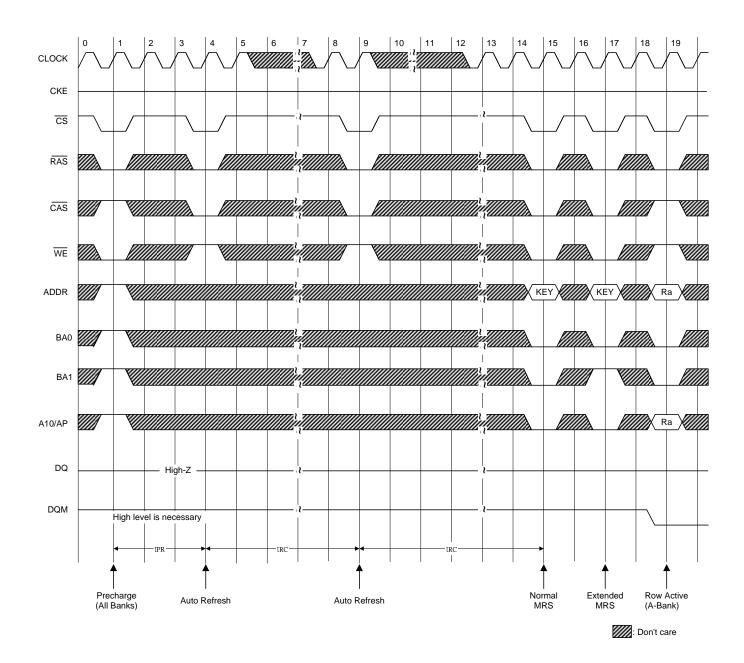

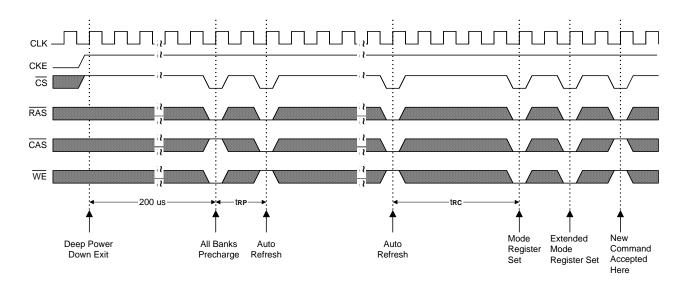

#### **Power Up Sequence**

- 1. Apply power and start clock, Attempt to maintain CKE = "H", DQM = "H" and the other pins are NOP condition at inputs.

- 2. Maintain stable power, stable clock and NOP input condition for a minimum of  $200 \mu s$ .

- 3. Issue precharge commands for all banks of the devices.

- 4. Issue 2 or more auto-refresh commands.

- 5. Issue a mode register set command to initialize the mode register. The device is now ready for normal operation.

- 6. Issue a extended mode register set command to define DS or PASR operating type of the device after normal MRS.

- cf.) Sequence of 4 & 5 may be changed.

- EMRS cycle is not mandatory and the EMRS command needs to be issued only when DS or PASR is used.

- The default state without EMRS command issued is the half driver strength and full array refreshed.

- The device is now ready for the operation selected by EMRS.

- For operating with DS or PASR, set DS or PASR mode in EMRS setting stage.

In order to adjust another mode in the state of DS or PASR mode, additional EMRS set is required but power up sequence is not needed again at this time. In that case, all banks have to be in idle state prior to adjusting EMRS set.

#### Burst Sequence (Burst Length = 4)

| Initial a | address |   | Com  | ential |   | Interleave |   |   |   |  |  |

|-----------|---------|---|------|--------|---|------------|---|---|---|--|--|

| A1        | A0      |   | Sequ | ential |   |            |   |   |   |  |  |

| 0         | 0       | 0 | 1    | 1      | 2 | 3          |   |   |   |  |  |

| 0         | 1       | 1 | 2    | 3      | 0 | 1          | 0 | 3 | 2 |  |  |

| 1         | 0       | 2 | 3    | 0      | 1 | 2          | 3 | 0 | 1 |  |  |

| 1         | 1       | 3 | 0    | 1      | 2 | 3          | 2 | 1 | 0 |  |  |

#### Burst Sequence (Burst Length = 8)

| Initi | al add | ress |   |            |   | Com | antial |   |   |   |   |   |            | Inter |   |   |   |   |

|-------|--------|------|---|------------|---|-----|--------|---|---|---|---|---|------------|-------|---|---|---|---|

| A2    | A1     | A0   |   | Sequential |   |     |        |   |   |   |   |   | Interleave |       |   |   |   |   |

| 0     | 0      | 0    | 0 | 1          | 2 | 3   | 4      | 5 | 6 | 7 | 0 | 1 | 2          | 3     | 4 | 5 | 6 | 7 |

| 0     | 0      | 1    | 1 | 2          | 3 | 4   | 5      | 6 | 7 | 0 | 1 | 0 | 3          | 2     | 5 | 4 | 7 | 6 |

| 0     | 1      | 0    | 2 | 3          | 4 | 5   | 6      | 7 | 0 | 1 | 2 | 3 | 0          | 1     | 6 | 7 | 4 | 5 |

| 0     | 1      | 1    | 3 | 4          | 5 | 6   | 7      | 0 | 1 | 2 | 3 | 2 | 1          | 0     | 7 | 6 | 5 | 4 |

| 1     | 0      | 0    | 4 | 5          | 6 | 7   | 0      | 1 | 2 | 3 | 4 | 5 | 6          | 7     | 0 | 1 | 2 | 3 |

| 1     | 0      | 1    | 5 | 6          | 7 | 0   | 1      | 2 | 3 | 4 | 5 | 4 | 7          | 6     | 1 | 0 | 3 | 2 |

| 1     | 1      | 0    | 6 | 7          | 0 | 1   | 2      | 3 | 4 | 5 | 6 | 7 | 4          | 5     | 2 | 3 | 0 | 1 |

| 1     | 1      | 1    | 7 | 0          | 1 | 2   | 3      | 4 | 5 | 6 | 7 | 6 | 5          | 4     | 3 | 2 | 1 | 0 |

#### **Device Operations**

#### Clock (CLK)

The clock input is used as the reference for all SDRAM operations. All operations are synchronized to the positive going edge of the clock. The clock transitions must be monotonic between VIL and VIH. During operation with CKE high all inputs are assumed to be in valid state (low or high) for the duration of set up and hold time around positive edge of the clock for proper functionality and ICC specifications.

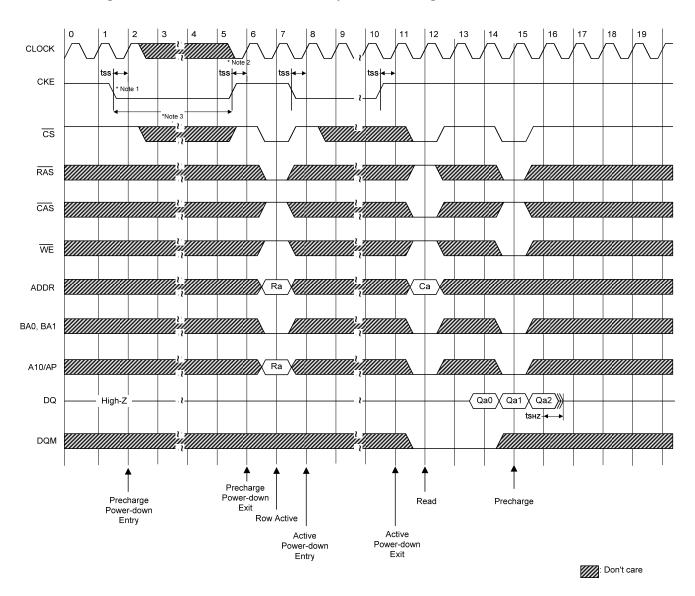

#### Clock Enable (CKE)

The clock enable (CKE) gates the clock onto SDRAM. If CKE goes low synchronously with clock (set-up and hold time same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. When all banks are in the idle state and CKE goes low synchronously with clock, the SDRAM enters the power down mode from the next clock cycle. The SDRAM remains in the power down mode ignoring the other inputs as long as CKE remains low. The power down exit is synchronous as the internal clock is suspended. When CKE goes high at least "tSS + 1 CLOCK" before the high going edge of the clock, then the SDRAM becomes active from the same clock edge accepting all the input commands.

#### Bank Select (BA0, BA1)

This SDRAM is organized as 4 independent banks of 524,288 words X 32 bits memory arrays. The BA0, BA1 inputs is latched at the time of assertion of  $\overline{RAS}$  and  $\overline{CAS}$  to select the bank to be used for the operation. The bank select BA0, BA1 is latched at bank activate, read, write mode register set and precharge operations.

#### Address Input (A0 ~ A10/AP)

The 19 address bits required to decode the 524,288 word locations are multiplexed into 11 address input pins (A0~A10/AP). The 11 bit row address is latched along with  $\overline{RAS}$ , BA0 and BA1 during bank activate command. The 8 bit column address is latched along with  $\overline{CAS}$ ,  $\overline{WE}$ , BA0 and BA1 during read or write command.

#### **NOP and Device Deselect**

When  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  are high, the SDRAM performs no operation (NOP). NOP does not initiate any new operation, but is needed to complete operations which require more than single clock like bank activate, burst read, auto refresh, etc. The device deselect is also a NOP and is entered by asserting  $\overline{CS}$  high.  $\overline{CS}$  high disables the command decoder so that  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$ , and all the address inputs are ignored.

#### Power-Up

The following sequence is recommended for POWER UP

1. Power must be applied to either CKE and DQM inputs to pull them high and other pins are NOP condition at the inputs before or along with VDD (and VDDQ) supply.

The clock signal must also be asserted at the same time.

- 2. After VDD reaches the desired voltage, a minimum pause of 200 microseconds is required with inputs in NOP condition.

- 3. All banks must be precharged now.

- 4. Perform a minimum of 2 Auto refresh cycles to stabilize the internal circuitry.

- 5. Perform a MODE REGISTER SET cycle to program the CAS latency, burst length and burst type as the default value of mode register is undefined.

At the end of one clock cycle from the mode register set cycle, the device is ready for operation.

When the above sequence is used for Power-up, all the out-puts will be in high impedance state. The high impedance of outputs is not guaranteed in any other power-up sequence.

cf.) Sequence of 4 & 5 may be changed.

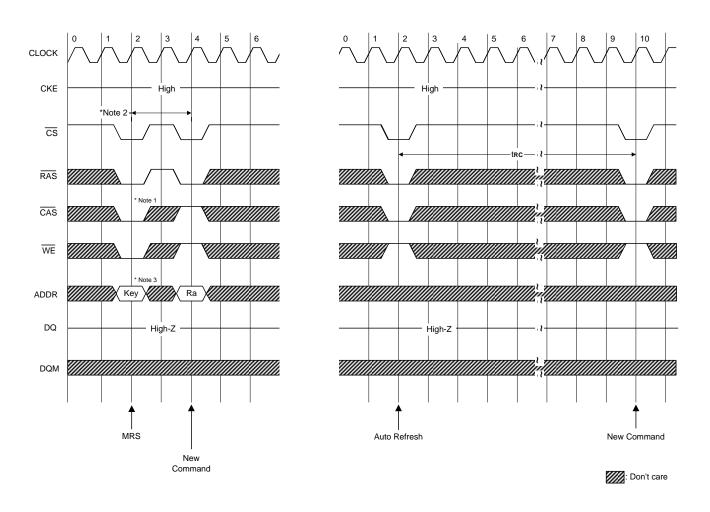

#### Mode Register Set (MRS)

The mode register stores the data for controlling the various operation modes of SDRAM. It programs the CAS latency, addressing mode, burst length, test mode and various vendor specific options to make SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after power up to operate the SDRAM. The mode register is written by asserting low on  $\overline{CS}$  ,  $\overline{RAS}$  ,  $\overline{CAS}$  , WE (The SDRAM should be in active mode with CKE already high prior to writing the mode register). The state of address pins A0~A10/AP, BA0 and BA1 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  going low is the data written in the mode register. One clock cycle is required to complete the write in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length field uses A0~A2, burst type uses A3, addressing mode uses A4~A6, A7~A8, A10/AP, BA0 and BA1 are used for vendor specific options or test mode. And the write burst length is programmed using A7~A9, A10/AP, BA0 and BA1 must be set to low for normal SDRAM operation.

Refer to table for specific codes for various burst length, addressing modes and CAS latencies. BA0 and BA1 have to be set to "0" to enter the Mode Register.

#### Extended Mode Register (EMRS)

The Extended Mode Register controls functions beyond those controlled by the Mode Register. These additional functions are unique to AMIC's Low Power SDRAM and includes a Partial-Array Self Refresh field (PASR) and Output Drive Strength. The Extended Mode Register is programmed via the Mode Register Set command (BA=1, BA0=0) and retains the stored information until it is programmed again or the device loses power. The Extended Mode Register must be programmed with A8 through A10 set to "0". The Extended Mode Register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time initiating any subsequent operation. Violating either of these requirements results in unspecified operation.

#### Auto Temperature Compensated Self Refresh

Every cell in the DRAM requires refreshing due to the capacitor losing its charge over time. The refresh rate is dependent on temperature. At higher temperatures a capacitor loses charge quicker than at lower temperature, requiring the cells to be refreshed more often. In order to save power consumption, according to the temperature, Mobile-SDRAM includes the internal temperature sensor and control units to control the self refresh cycle automatically.

#### Partial Array Self Refresh

The Partial Array Self Refresh (PASR) feature allows the controller to select the amount of memory that will be refreshed during SELF REFRESH. The refresh options are all banks (banks 0, 1, 2, and 3); two banks (banks 0 and 1 or 2 and 3 by A7); and one bank (bank 0 or 2 by A7). WRITE and READ commands occur to any bank selected during standard operation, but only the selected banks in PASR will be refreshed during SELF REFRESH. The data in banks 2 and 3 will be lost when the two bank option with A7=0 is used. Similarly the data will be lost in banks 1, 2, and 3 when the one bank option with A7=0 is used down.

#### **Driver Strength Control**

The driver strength feature allows one to reduce the drive strength of the I/O's on the device during low frequency operation. This allows systems to reduce the noise associated with the I/O's switching.

#### **Bank Activate**

The bank activate command is used to select a random row in an idle bank. By asserting low on RAS and CS with desired row and bank addresses, a row access is initiated. The read or write operation can occur after a time delay of tRCD(min) from the time of bank activation. tRCD(min) is an internal timing parameter of SDRAM, therefore it is dependent on operating clock frequency. The minimum number of clock cycles required between bank activate and read or write command should be calculated by dividing tRCD(min) with cycle time of the clock and then rounding off the result to the next higher integer. The SDRAM has 4 internal banks on the same chip and shares part of the internal circuitry to reduce chip area, therefore it restricts the activation of all banks simultaneously. Also the noise generated during sensing of each bank of SDRAM is high requiring some time for power supplies to recover before the other bank can be sensed reliably. trrd(min) specifies the minimum time required between activating different banks. The number of clock cycles required between different bank activation must be calculated similar to tRCD specification. The minimum time required for the bank to be active to initiate sensing and restoring the complete row of dynamic cells is determined by tras(min) specification before a precharge command to that active bank can be asserted. The maximum time any bank can be in the active state is determined by tras(max). The number of cycles for both tras(min) and tras(max) can be calculated similar to trcd specification.

#### Burst Read

The burst read command is used to access burst of data on consecutive clock cycles from an active row in an active bank. The burst read command is issued by asserting low on CS and  $\overline{CAS}$  with WE being high on the positive edge of the clock. The bank must be active for at least trcp(min) before the burst read command is issued. The first output appears CAS latency number of clock cycles after the issue of burst read command. The burst length, burst sequence and latency from the burst read command is determined by the mode register which is already programmed. The burst read can be initiated on any column address of the active row. The address wraps around if the initial address does not start from a boundary such that number of outputs from each I/O are equal to the burst length programmed in the mode register. The output goes into high-impedance at the end of the burst, unless a new burst read was initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read or burst write in the same bank or the other active bank or a precharge command to the same bank. The burst stop command is valid at every page burst length.

#### **Burst Write**

The burst write command is similar to burst read command, and is used to write data into the SDRAM consecutive clock cycles in adjacent addresses depending on burst length and burst sequence. By asserting low on CS, CAS and WE with valid column address, a write burst is initiated. The data inputs are provided for the initial address in the same clock cycle as the burst write command. The input buffer is deselected at the end of the burst length, even though the internal writing may not have been completed yet. The burst write can be terminated by issuing a burst read and DQM for blocking data inputs or burst write in the same or the other active bank. The burst stop command is valid only at full page burst length where the writing continues at the end of burst and the burst is wrap around. The write burst can also be terminated by using DQM for blocking data and precharging the bank "trot." after the last data input to be written into the active row. See DQM OPERATION also.

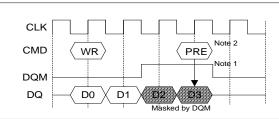

#### **DQM Operation**

The DQM is used to mask input and output operation. It works similar to  $\overline{OE}$  during read operation and inhibits writing during write operation. The read latency is two cycles from DQM and zero cycle for write, which means DQM masking occurs two cycles later in the read cycle and occurs in the same cycle during write cycle. DQM operation is synchronous with the clock, therefore the masking occurs for a complete cycle. The DQM signal is important during burst interrupts of write with read or precharge in the SDRAM. Due to asynchronous nature of the internal write, the DQM operation is critical to avoid unwanted or incomplete writes when the complete burst write is not required.

#### Precharge

The precharge operation is performed on an active bank by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{WE}$  and A10/AP with valid BA of the bank to be precharged. The precharge command can be asserted anytime after tras(min) is satisfied from the bank activate command in the desired bank. "trap" is defined as the minimum time required to precharge a bank.

The minimum number of clock cycles required to complete row precharge is calculated by dividing "tree" with clock cycle

time and rounding up to the next higher integer. Care should be taken to make sure that burst write is completed or DQM is used to inhibit writing before precharge command is asserted. The maximum time any bank can be active is specified by  $t_{RAS}(max)$ . Therefore, each bank has to be precharged within  $t_{RAS}(max)$  from the bank activate command. At the end of precharge, the bank enters the idle state and is ready to be activated again.

Entry to Power Down, Auto refresh, Self refresh and Mode register Set etc, is possible only when all banks are in idle state.

#### **Auto Precharge**

The precharge operation can also be performed by using auto precharge. The SDRAM internally generates the timing to satisfy tRAS(min) and "tRP" for the programmed burst length and CAS latency. The auto precharge command is issued at the same time as burst read or burst write by asserting high on A10/AP. If burst read or burst write command is issued with low on A10/AP, the bank is left active until a new command is asserted. Once auto precharge command is given, no new commands are possible to that particular bank until the bank achieves idle state.

#### All Banks Precharge

All banks can be precharged at the same time by using Precharge all command. Asserting low on  $\overline{CS}$ ,  $\overline{RAS}$  and

$\overline{\text{WE}}$  with high on A10/AP after both banks have satisfied tras(min) requirement, performs precharge on all banks. At the end of tRP after performing precharge all, all banks are in idle state.

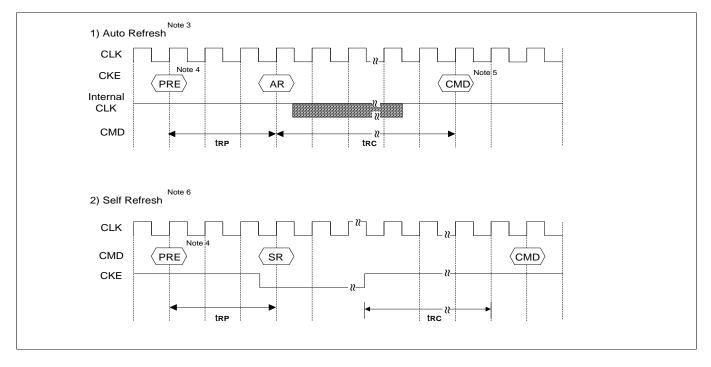

#### Auto Refresh

The storage cells of SDRAM need to be refreshed every 64ms to maintain data. An auto refresh cycle accomplishes refresh of a single row of storage cells. The internal counter increments automatically on every auto refresh cycle to refresh all the rows. An auto refresh command is issued by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{CAS}$  with high on CKE and  $\overline{WE}$ . The auto refresh command can only be asserted with all banks being in idle state and the device is not in power down mode (CKE is high in the previous cycle). The

time required to complete the auto refresh operation is specified by " $t_{RC}(min)$ ". The minimum number of clock cycles required can be calculated by dividing " $t_{RC}$ " with clock cycle time and then rounding up to the next higher integer. The auto refresh command must be followed by NOP's until the auto refresh operation is completed. All banks will be in the idle state at the end of auto refresh operation. The auto refresh is the preferred refresh mode when the SDRAM is being used for normal data transactions. The auto refresh cycle can be performed once in 15.6us or a burst of 4096 auto refresh cycles once in 64ms.

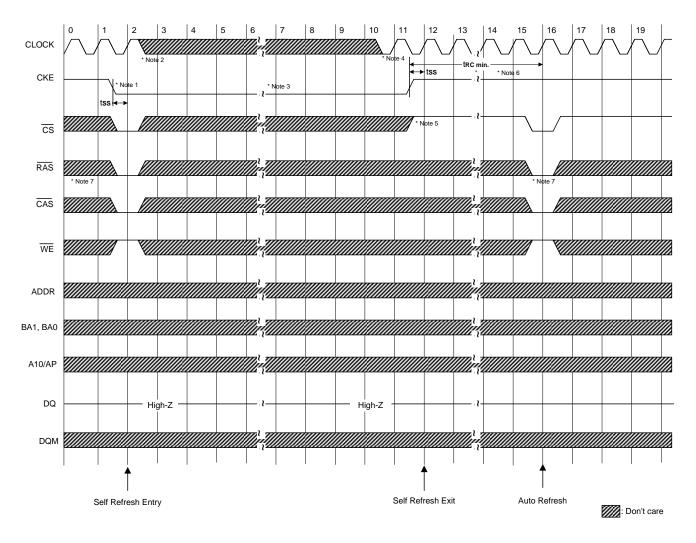

#### Self Refresh

The self refresh is another refresh mode available in the SDRAM. The self refresh is the preferred refresh mode for data retention and low power operation of SDRAM. In self refresh mode, the SDRAM disables the internal clock and all the input buffers except CKE. The refresh addressing and timing is internally generated to reduce power consumption.

The self refresh mode is entered from all banks idle state by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE with high on  $\overline{WE}$ . Once the self refresh mode is entered, only CKE state being low matters, all the other inputs including clock are ignored to remain in the self refresh.

The self refresh is exited by restarting the external clock and then asserting high on CKE. This must be followed by NOP's for a minimum time of "t<sub>R</sub>c" before the SDRAM reaches idle state to begin normal operation. Upon exiting the self refresh mode, AUTO REFRESH commands must be issued every 15.6  $\mu$  s or less as both SELF REFRESH and AUTO REFRESH utilize the row refresh counter.

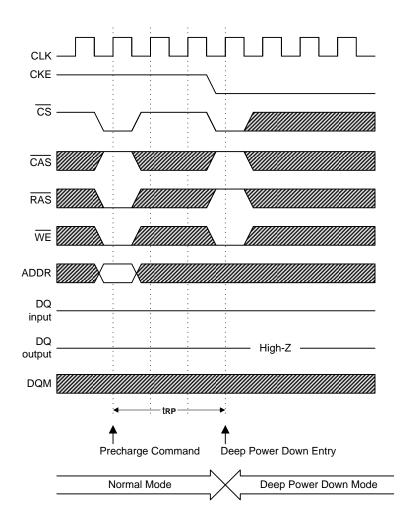

#### Deep Power Down Mode

The Deep Power Down Mode is an unique function on Low Power SDRAMs with very low standby currents. All internal voltage generators inside the Low Power SDRAMs are stopped and all memory data will be lost in this mode. To enter the Deep Power Down Mode all banks must be precharged and the necessary Precharged Delay tree must occur.

#### **Basic feature And Function Descriptions**

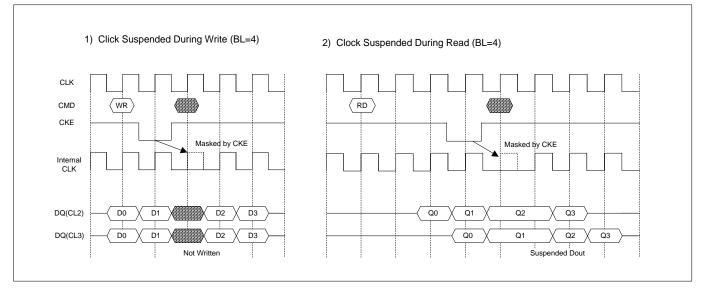

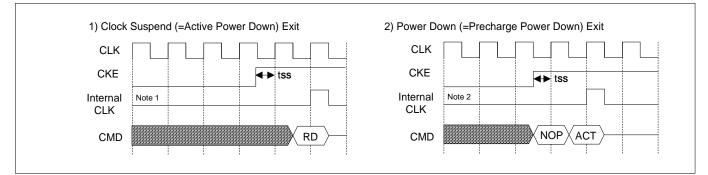

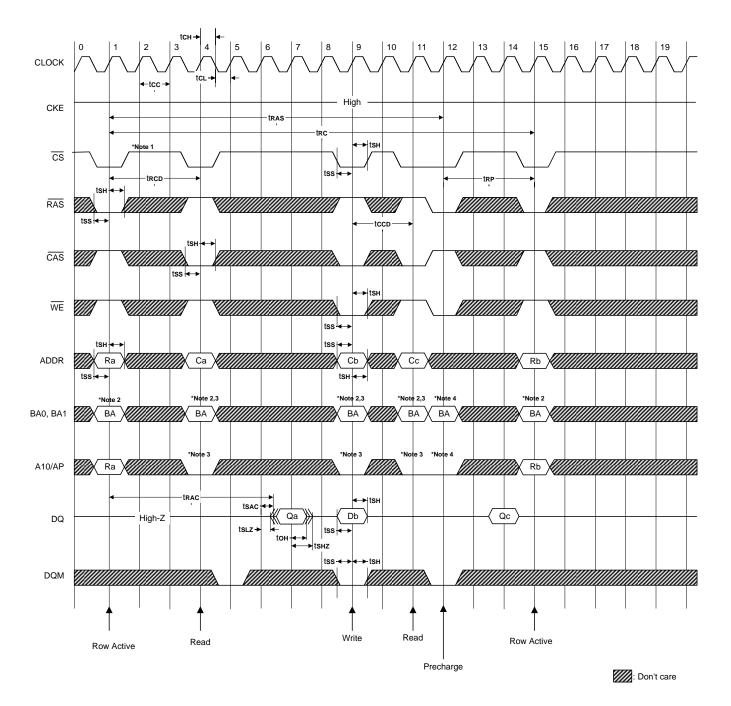

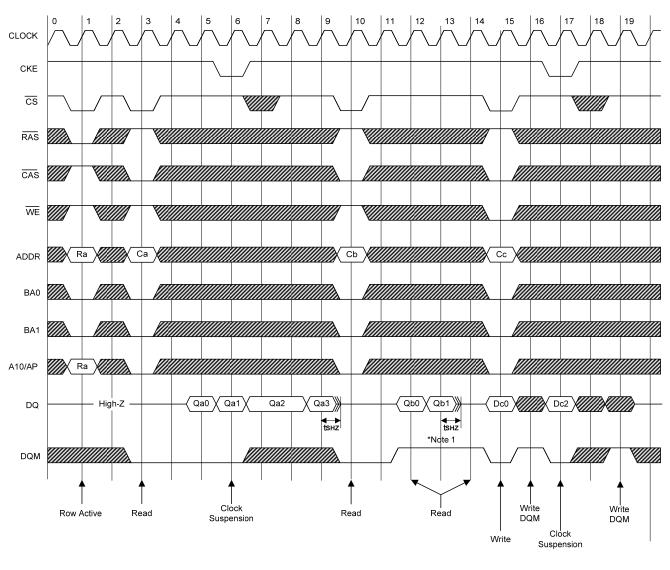

#### 1. CLOCK Suspend

Note: CLK to CLK disable/enable=1 clock

#### 2. DQM Operation

\* **Note :** 1. DQM makes data out Hi-Z after 2 clocks which should masked by CKE "L". 2. DQM masks both data-in and data-out.

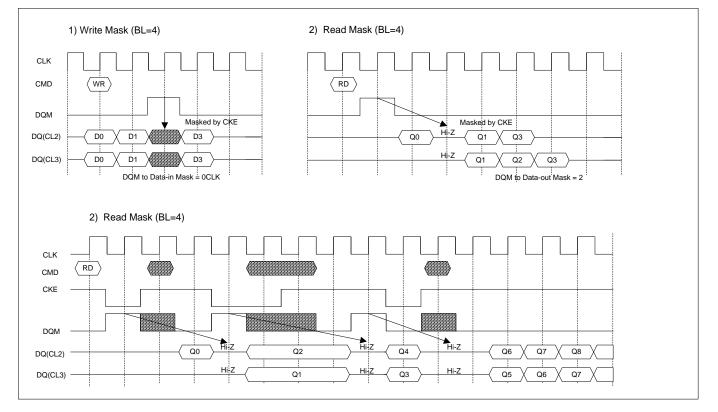

#### 3. CAS Interrupt (I)

Note : 1. By "Interrupt", It is possible to stop burst read/write by external command before the end of burst.

By " $\overline{CAS}$  Interrupt", to stop burst read/write by  $\overline{CAS}$  access; read, write and block write.

- 2. tccd :  $\overline{CAS}$  to  $\overline{CAS}$  delay. (=1CLK)

- 3. tcpL : Last data in to new column address delay. (= 1CLK).

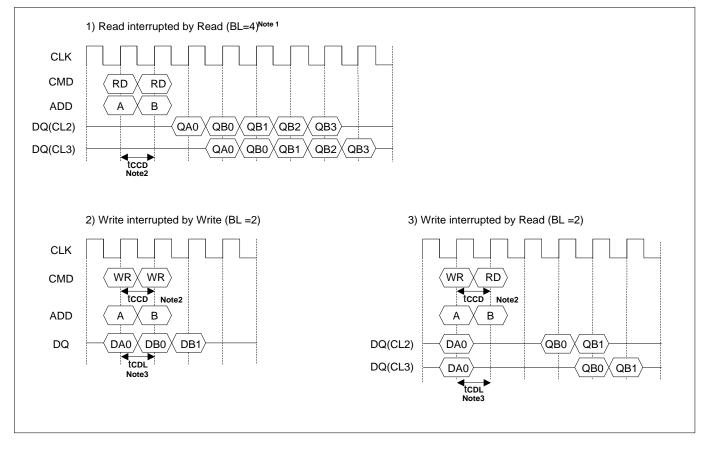

#### 4. CAS Interrupt (II) : Read Interrupted Write & DQM

\* Note : 1. To prevent bus contention, there should be at least one gap between data in and data out.

2. To prevent bus contention, DQM should be issued which makes a least one gap between data in and data out.

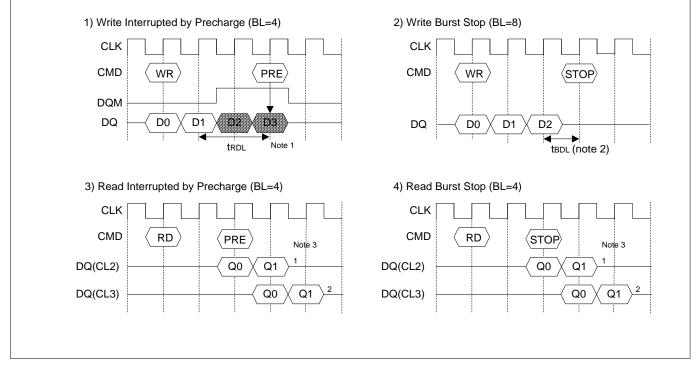

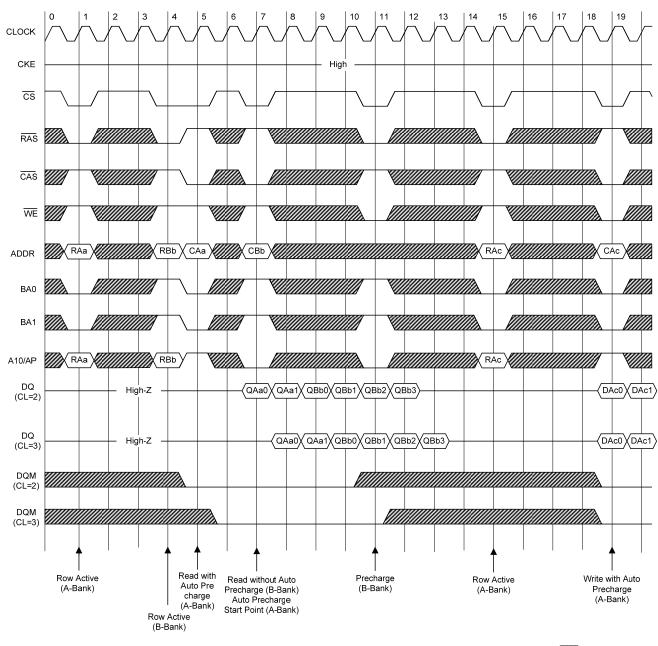

#### 5. Write Interrupted by Precharge & DQM

Note : 1. To inhibit invalid write, DQM should be issued.

2. This precharge command and burst write command should be of the same bank, otherwise it is not precharge interrupt but only another bank precharge of dual banks operation.

#### 6. Precharge

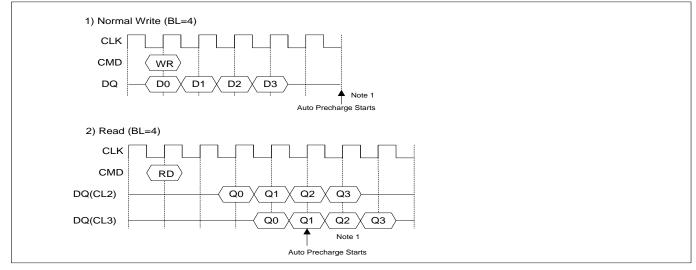

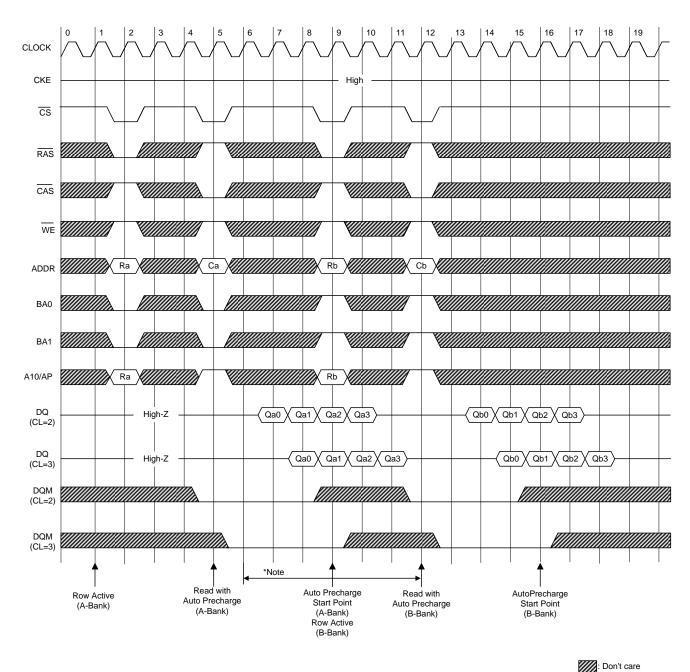

#### 7. Auto Precharge

\* Note : 1. The row active command of the precharge bank can be issued after tree from this point. The new read/write command of other active bank can be issued from this point. At burst read/write with auto precharge, CAS interrupt of the same/another bank is illegal.

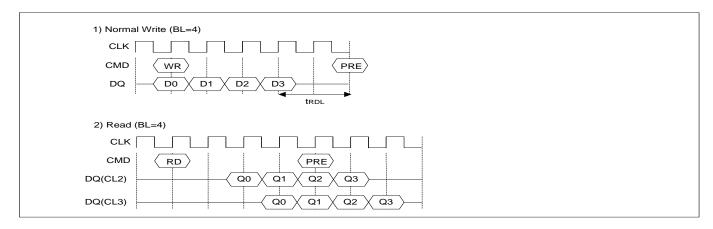

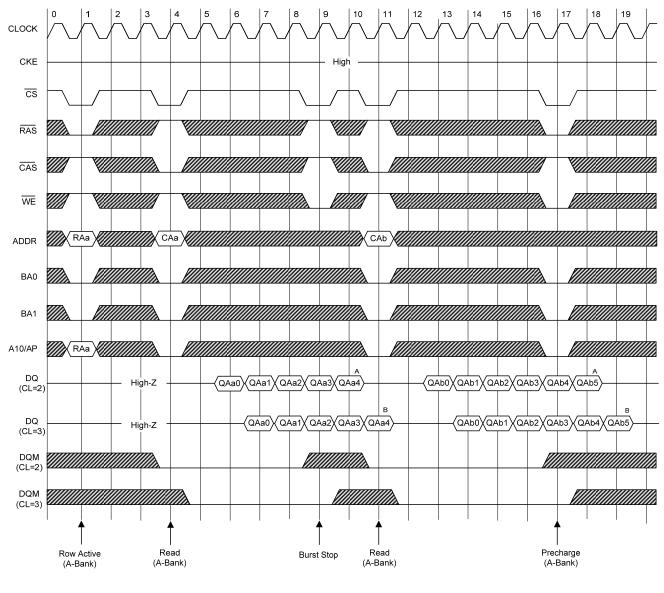

#### 8. Burst Stop & Precharge Interrupt

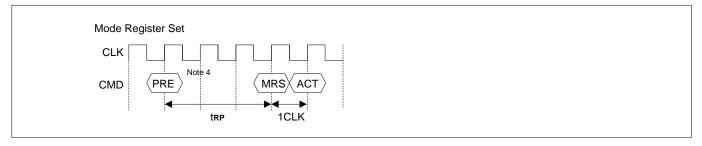

#### 9. MRS

- Note : 1. tRDL : 2CLK, Last Data in to Row Precharge.

- 2. tBDL : 1CLK, Last Data in to Burst Stop Delay.

- 3. Number of valid output data after Row precharge or burst stop : 1,2 for CAS latency=2,3 respectively.

- 4. PRE : All banks precharge if necessary.

- MRS can be issued only at all bank precharge state.

#### 10. Clock Suspend Exit & Power Down Exit

#### 11. Auto Refresh & Self Refresh

- \* Note : 1. Active power down : one or more bank active state.

- 2. Precharge power down : both bank precharge state.

- 3. The auto refresh is the same as CBR refresh of conventional DRAM. No precharge commands are required after Auto Refresh command. During trc from auto refresh command, any other command can not be accepted.

- 4. Before executing auto/self refresh command, both banks must be idle state.

- 5. MRS, Bank Active, Auto/Self Refresh, Power Down Mode Entry.

- 6. During self refresh mode, refresh interval and refresh operation are performed internally. After self refresh entry, self refresh mode is kept while CKE is LOW. During self refresh mode, all inputs expect CKE will be don't cared, and outputs will be in Hi-Z state. During trc from self refresh exit command, any other command can not be accepted. Before/After self refresh mode, AUTO REFRESH commands must be issued every 15.6 μ s or less as both SELF REFRESH and AUTO REFRESH utilize the row refresh counter.

# 12. About Burst Type Control

| Basic<br>MODE  | Sequential counting                  | At MRS A3="0". See the BURST SEQUENCE TABE.(BL=4,8)<br>BL=1,2,4,8 and full page wrap around.                                                                            |  |  |  |  |  |

|----------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MODE           | Interleave counting                  | At MRS A3=" 1". See the BURST SEQUENCE TABE.(BL=4,8)<br>BL=4,8 At BL=1,2 Interleave Counting = Sequential Counting                                                      |  |  |  |  |  |

| Random<br>MODE | Random column Access<br>tccp = 1 CLK | Every cycle Read/Write Command with random column address can realize Random Column Access.<br>That is similar to Extended Data Out (EDO) Operation of convention DRAM. |  |  |  |  |  |

# 13. About Burst Length Control

|                   |               | At MRS A2,1,0 = "000".<br>At auto precharge, tRAS should not be violated.                                                                                                                                                                                                   |  |  |  |  |  |

|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Basic<br>MODE     |               | At MRS A2,1,0 = "001".<br>At auto precharge, tRAS should not be violated.                                                                                                                                                                                                   |  |  |  |  |  |

|                   | 4             | At MRS A2,1,0 = "010"                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                   | 8             | At MRS A2,1,0 = "011".                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Special<br>MODE   |               | At MRS A9="1".<br>Read burst = 1,2,4,8, full page/write Burst =1<br>At auto precharge of write, tRAS should not be violated.                                                                                                                                                |  |  |  |  |  |

| Interrupt<br>MODE |               | Before the end of burst, Row precharge command of the same bank<br>Stops read/write burst with Row precharge.<br>tRDL= 2 with DQM, valid DQ after burst stop is 1,2 for CL=2,3 respectively<br>During read/write burst with auto precharge, RAS interrupt cannot be issued. |  |  |  |  |  |

| MODE              | CAS Interrupt | Before the end of burst, new read/write stops read/write burst and starts new read/write burst or block write.<br>During read/write burst with auto precharge, $\overline{CAS}$ interrupt can not be issued.                                                                |  |  |  |  |  |

#### Power On Sequence & Auto Refresh

### Single Bit Read-Write-Read Cycles (Same Page) @CAS Latency=3, Burst Length=1

\* Note : 1. All inputs can be don't care when CS is high at the CLK high going edge.

2. Bank active & read/write are controlled by BA0, BA1.

| BA1 | BA0 | Active & Read/Write |

|-----|-----|---------------------|

| 0   | 0   | Bank A              |

| 0   | 1   | Bank B              |

| 1   | 0   | Bank C              |

| 1   | 1   | Bank D              |

3. Enable and disable auto precharge function are controlled by A10/AP in read/write command.

| A10/AP | BA1 | BA0 | Operation                                                    |

|--------|-----|-----|--------------------------------------------------------------|

|        | 0   | 0   | Disable auto precharge, leave bank A active at end of burst. |

| 0      | 0   | 1   | Disable auto precharge, leave bank B active at end of burst. |

| 0      | 1   | 0   | Disable auto precharge, leave bank C active at end of burst. |

| 1      |     | 1   | Disable auto precharge, leave bank D active at end of burst. |

|        | 0   | 0   | Enable auto precharge, precharge bank A at end of burst.     |

|        | 0   | 1   | Enable auto precharge, precharge bank B at end of burst.     |

| 1      | 1   | 0   | Enable auto precharge, precharge bank C at end of burst.     |

|        | 1   | 1   | Enable auto precharge, precharge bank D at end of burst.     |

4. A10/AP and BA0, BA1 control bank precharge when precharge command is asserted.

| A10/AP | BA1 | BA0 | Precharge |

|--------|-----|-----|-----------|

| 0      | 0   | 0   | Bank A    |

| 0      | 0   | 1   | Bank B    |

| 0      | 1   | 0   | Bank C    |

| 0      | 1   | 1   | Bank D    |

| 1      | Х   | Х   | All Banks |

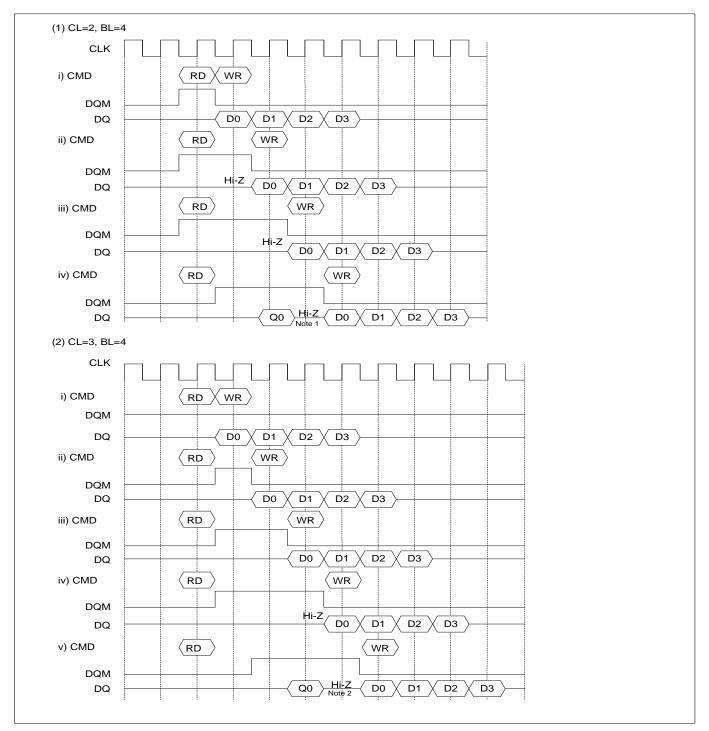

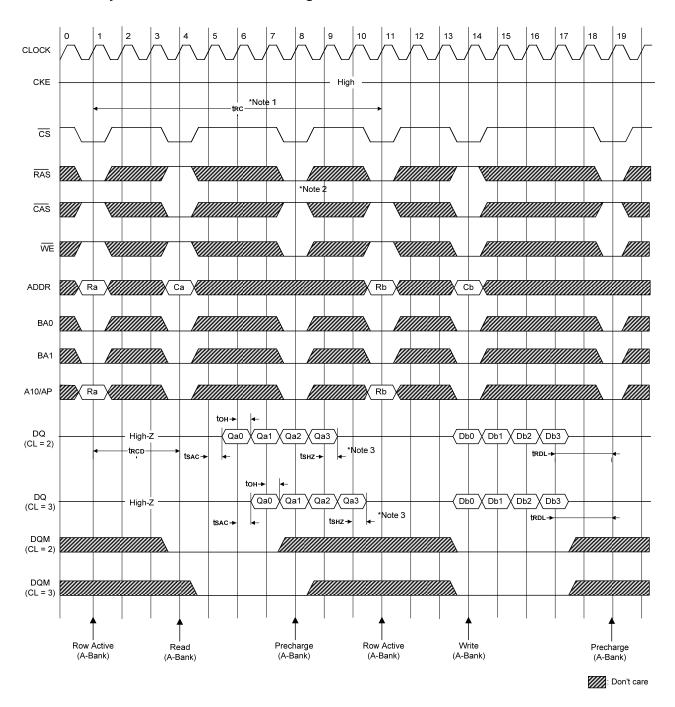

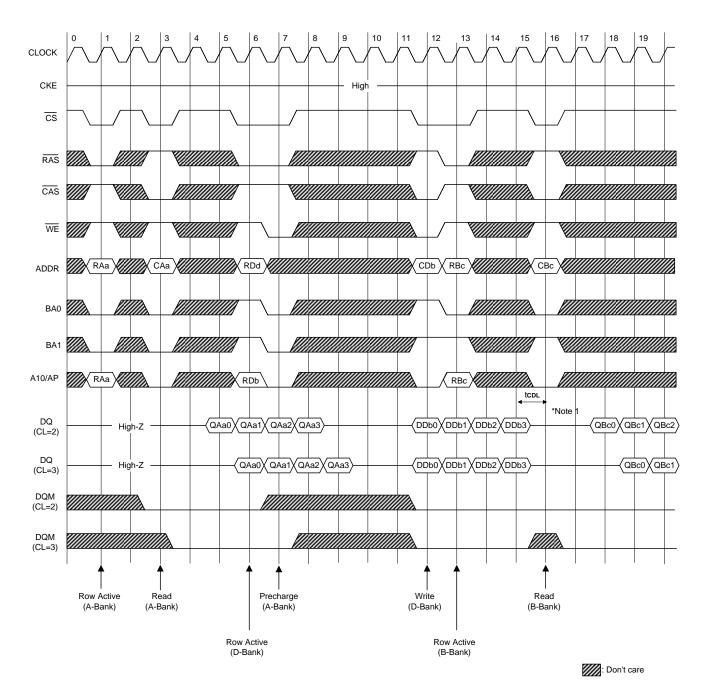

#### Read & Write Cycle at Same Bank @Burst Length=4

\*Note : 1. Minimum row cycle times is required to complete internal DRAM operation.

- 2. Row precharge can interrupt burst on any cycle. [CAS latency-1] number of valid output data is available after Row precharge. Last valid output will be Hi-Z(tsHz) after the clock.

- 3. Output will be Hi-Z after the end of burst. (1, 2, 4, 8 & Full page bit burst)

#### Page Read & Write Cycle at Same Bank @Burst Length=4, tRDL=2CLK

- \*Note : 1. To write data before burst read ends, DQM should be asserted three cycle prior to write command to avoid bus contention.

- 2. Row precharge will interrupt writing. Last data input, tRDL before Row precharge, will be written.

- 3. DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

- 4. tDAL, last data in to active delay, is tRDL + tRP.

25

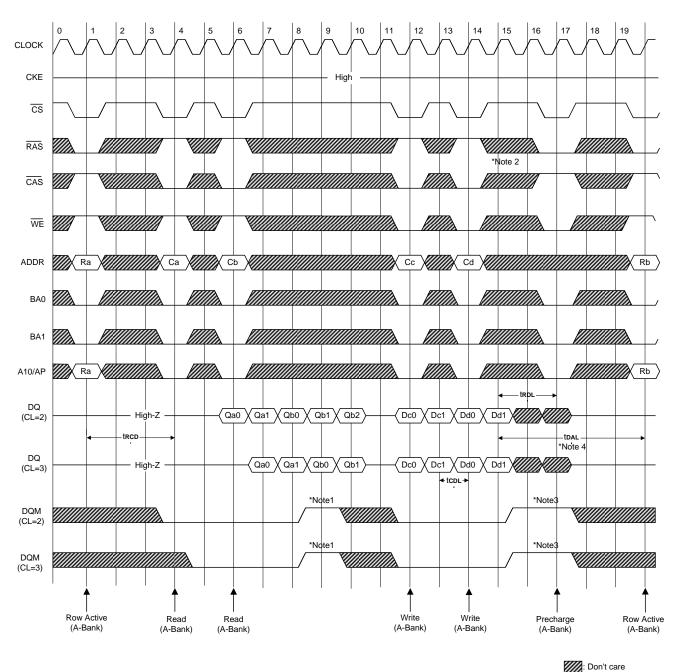

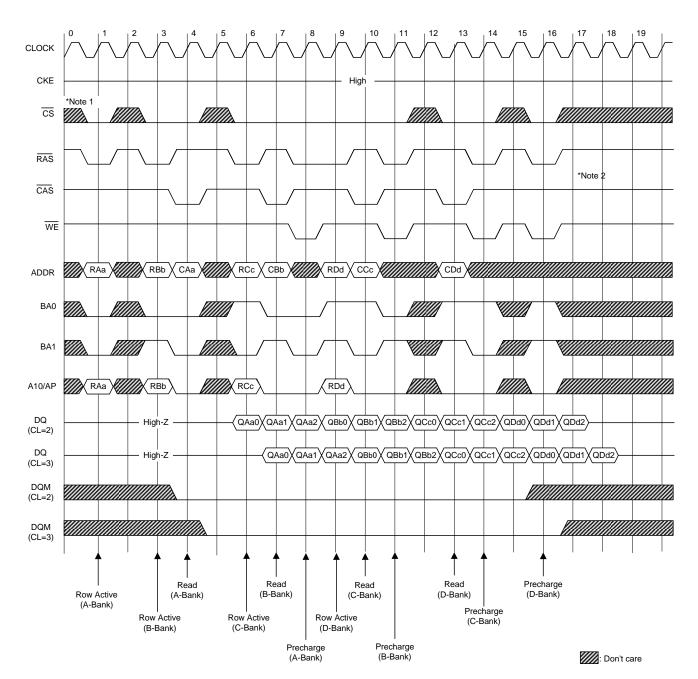

#### Page Read Cycle at Different Bank @Burst Length = 4

\* Note : 1. CS can be don't cared when RAS, CAS and WE are high at the clock high going edge.

2. To interrupt a burst read by row precharge, both the read ad the precharge banks must be the same.

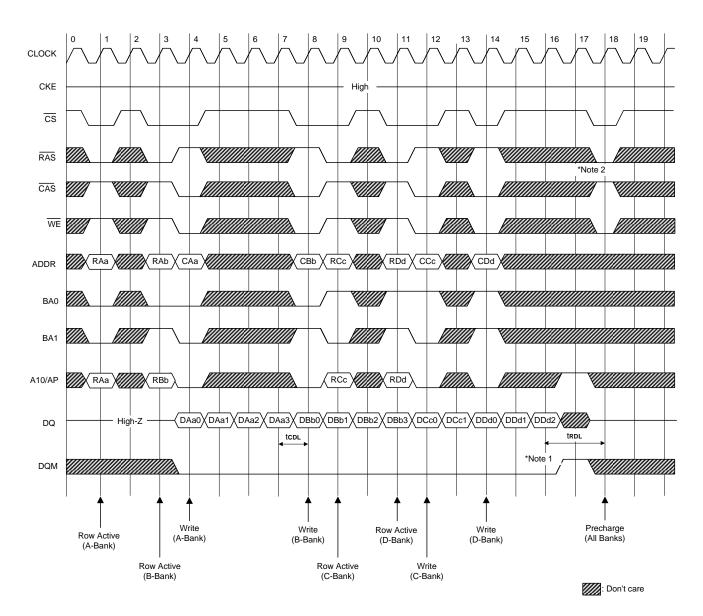

### Page Write Cycle at Different Bank @Burst Length=4, tRDL=2CLK

\* Note:

1. To interrupt burst write by Row precharge, DQM should be asserted to mask invalid input data.

2. To interrupt burst write by Row precharge, both the write and precharge banks must be the same.

\* Note : tcpL should be met to complete write.

: Don't care

\*Note : When Read (Write) command with auto precharge is issued at A-Bank after A and B Bank activation.

- if Read (Write) command without auto precharge is issued at B-Bank before A-Bank auto precharge starts, A-Bank auto precharge will start at B-Bank read command input point.

- any command can not be issued at A-Bank during trp after A-Bank auto precharge starts.

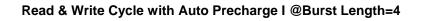

#### Read & Write Cycle with Auto Precharge II @Burst Length=4

\* Note : Any command to A-bank is not allowed in this period. tRP is determined from at auto precharge start point.

## Clock Suspension & DQM Operation Cycle @CAS Latency=2, Burst Length=4

: Don't care

\* Note : DQM is needed to prevent bus contention.

#### Read Interrupted by Precharge & Read Burst Stop Cycle @Full Page Burst

: Don't care

- $^{\ast}$  Note : 1. At full page mode, burst is finished by burst stop or precharge.

- About the valid DQs after burst stop, it is same as the case of Precharge interrupt.

Both cases are illustrated above timing diagram. See the label A, B on them.

But at burst write, Burst stop and Precharge interrupt should be compared carefully.

Refer the timing diagram of "Full page write burst stop cycle".

- 3. Burst stop is valid at every burst length.

#### 10 12 13 14 15 16 18 CLOCK CKE High CS RAS CAS WE ADDR BA0 BA1 A10/AP RAa X tBDL trdl Note 1 Note 1 2 DAa0 XDAa1 XDAa2 XDAa3 XDAa4 DQ High-Ż DQM Write Write Precharge (A-Bank) Row Active Burst Stop (A-Bank) (A-Bank) (A-Bank) : Don't care

#### Write Interrupted by Precharge Command & Write Burst Stop Cycle @Full Page Bust, tRDL=2CLK

\* Note : 1. At full page mode, burst is finished by burst stop or precharge.

2. Data-in at the cycle of interrupted by precharge cannot be written into the corresponding memory cell. It is defined by AC parameter of tRDL.

DQM at write interrupted by precharge command is needed to prevent invalid write.

DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

3. Burst stop is valid at every burst length.

#### Active/Precharge Power Down Mode @CAS Latency=2, Burst Length=4

\* Note : 1. All banks should be in idle state prior to entering precharge power down mode.

2. CKE should be set high at least "1CLK + tss" prior to Row active command.

3. Cannot violate minimum refresh specification. (64ms)

#### Self Refresh Entry & Exit Cycle

#### \* Note : TO ENTER SELF REFRESH MODE

- 1.  $\overline{CS}$ ,  $\overline{RAS}$  &  $\overline{CAS}$  with CKE should be low at the same clock cycle.

- 2. After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

- 3. The device remains in self refresh mode as long as CKE stays "Low".

- (cf.) Once the device enters self refresh mode, minimum tRAS is required before exit from self refresh.

#### TO EXIT SELF REFRESH MODE

- 4. System clock restart and be stable before returning CKE high.

- 5.  $\overline{CS}$  starts from high.

- 6. Minimum tRC is required after CKE going high to complete self refresh exit.

- 7. Before/After self refresh mode, AUTO REFRESH commands must be issued every 15.6  $\mu$ s or less as both SELF REFRESH and AUTO REFRESH utilize the row refresh counter.

#### Mode Register Set Cycle

#### Auto Refresh Cycle

\* All banks precharge should be completed before Mode Register Set cycle and auto refresh cycle.

#### MODE REGISTER SET CYCLE

- \* Note : 1.  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  &  $\overline{WE}$  activation at the same clock cycle with address key will set internal mode register.

- 2. Minimum 2 clock cycles should be met before new  $\overline{RAS}$  activation.

- 3. Please refer to Mode Register Set table.

#### Deep Power Down Mode Entry

#### Deep Power Down Mode Exit

The deep power down mode is exited by asserting CKE high. After the exit, the following sequence is needed to enter a new command:

- 1. Maintain NOP input conditions for a minimum of  $200 \mu s$

- 2. Issue precharge commands for all banks of the device

- 3. Issue eight or more auto-refresh commands

- 4. Issue a mode register set command to initialize the mode register

- 5. Issue an extended mode register set command to initialize the extended mode register

# A43E16321

# Function Truth Table (Table 1)

| Current<br>State  | CS    | RAS | CAS | WE | BA | Address    | Action                                              | Note |

|-------------------|-------|-----|-----|----|----|------------|-----------------------------------------------------|------|

|                   | Н     | Х   | Х   | Х  | Х  | Х          | NOP                                                 |      |

|                   | L     | Н   | Н   | Н  | Х  | Х          | NOP                                                 |      |

|                   | L     | Н   | Н   | L  | Х  | Х          | ILLEGAL                                             | 2    |

|                   | L     | Н   | L   | Х  | BA | CA, A10/AP | ILLEGAL                                             | 2    |

| IDLE              | L     | L   | Н   | Н  | BA | RA         | Row Active; Latch Row Address                       |      |

|                   | L     | L   | Н   | L  | BA | PA         | NOP                                                 | 4    |

|                   | L     | L   | L   | Н  | Х  | Х          | Auto Refresh or Self Refresh                        | 5    |

|                   | L     | L   | L   | L  | (  | OP Code    | Mode Register Access                                | 5    |

|                   | Н     | Х   | Х   | Х  | Х  | Х          | NOP                                                 |      |

|                   | L     | Н   | Н   | Н  | Х  | Х          | NOP                                                 |      |

| Row               | L     | Н   | Н   | L  | Х  | Х          | ILLEGAL                                             | 2    |

| Active            | L     | Н   | L   | Н  | BA | CA,A10/AP  | Begin Read; Latch CA; Determine AP                  |      |

|                   | L     | Н   | L   | L  | BA | CA,A10/AP  | Begin Write; Latch CA; Determine AP                 |      |

|                   | L     | L   | Н   | Н  | BA | RA         | ILLEGAL                                             | 2    |

|                   | L     | L   | Н   | L  | BA | PA         | Precharge                                           |      |

|                   | L     | L   | L   | Х  | Х  | Х          | ILLEGAL                                             |      |

|                   | Н     | Х   | Х   | Х  | Х  | Х          | NOP(Continue Burst to End $\rightarrow$ Row Active) |      |

|                   | L     | Н   | Н   | Н  | Х  | Х          | NOP(Continue Burst to End $\rightarrow$ Row Active) |      |

|                   | L     | Н   | Н   | L  | Х  | Х          | Term burst →Row Active                              |      |

| Read              | L     | Н   | L   | Н  | BA | CA,A10/AP  | Term burst; Begin Read; Latch CA; Determine AP      | 3    |

|                   | L     | Н   | L   | L  | BA | CA,AP      | Term burst; Begin Write; Latch CA; Determine AP     | 3    |

|                   | L     | L   | Н   | Н  | BA | RA         | ILLEGAL                                             | 2    |

|                   | L     | L   | Н   | L  | BA | PA         | Term Burst; Precharge timing for Reads              | 3    |

|                   | L     | L   | L   | Х  | Х  | Х          | ILLEGAL                                             |      |

|                   | Н     | Х   | Х   | Х  | Х  | Х          | NOP(Continue Burst to End→Row Active)               |      |

|                   | L     | н   | Н   | Н  | Х  | х          | NOP(Continue Burst to End→Row Active)               |      |

|                   | L     | Н   | Н   | L  | Х  | Х          | ILLEGAL                                             |      |

| Write             | L     | Н   | L   | Н  | BA | CA,A10/AP  | Term burst; Begin Read; Latch CA; Determine AP      | 3    |

|                   | L     | н   | L   | L  | BA |            | Term burst; Begin Read; Latch CA; Determine AP      | 3    |

|                   | L     | L   | Н   | Н  | BA | RA         | ILLEGAL                                             | 2    |

|                   | L     | L   | Н   | L  | BA | A10/AP     | Term Burst; Precharge timing for Writes             | 3    |

|                   | L     | L   | L   | Х  | Х  | Х          | ILLEGAL                                             |      |

|                   | Н     | Х   | Х   | Х  | Х  | Х          | NOP(Continue Burst to End→Precharge)                |      |

| _                 | L     | Н   | Н   | Н  | Х  | Х          | NOP(Continue Burst to End→Precharge)                |      |

| Read with<br>Auto | L     | Н   | Н   | L  | Х  | Х          | ILLEGAL                                             |      |

| Precharge         | L     | Н   | L   | Н  | BA | CA,A10/AP  | ILLEGAL                                             | 2    |

| -                 |       | H   | L   | L  | BA | CA,A10/AP  | ILLEGAL                                             | 2    |

|                   |       | L   | H   | X  | BA | RA, PA     | ILLEGAL                                             | _    |

|                   | <br>L | L   | L   | X  | X  | X          | ILLEGAL                                             | 2    |

| Current<br>State | CS | RAS | CAS | WE | вА | Address   | Action                               | Note |

|------------------|----|-----|-----|----|----|-----------|--------------------------------------|------|

|                  | Н  | Х   | Х   | Х  | Х  | Х         | NOP(Continue Burst to End→Precharge) |      |

|                  | L  | Н   | Н   | Н  | Х  | Х         | NOP(Continue Burst to End→Precharge) |      |

| Write with       | L  | Н   | Н   | L  | Х  | Х         | ILLEGAL                              |      |

| Auto             | L  | Н   | L   | Н  | BA | CA,A10/AP | ILLEGAL                              | 2    |

| Precharge        | L  | Н   | L   | L  | BA | CA,A10/AP | ILLEGAL                              | 2    |

|                  | L  | L   | Н   | Х  | BA | RA, PA    | ILLEGAL                              |      |

|                  | L  | L   | L   | Х  | Х  | Х         | ILLEGAL                              | 2    |

|                  | Н  | Х   | Х   | Х  | Х  | Х         | NOP→Idle after tr₽                   |      |

|                  | L  | Н   | Н   | Н  | Х  | Х         | NOP→Idle after tr₽                   |      |

|                  | L  | Н   | Н   | L  | Х  | Х         | ILLEGAL                              |      |

| Precharge        | L  | Н   | L   | Х  | BA | CA,A10/AP | ILLEGAL                              | 2    |

|                  | L  | L   | Н   | Н  | BA | RA        | ILLEGAL                              | 2    |

|                  | L  | L   | Н   | L  | BA | PA        | NOP→Idle after t℞₽                   | 2    |

|                  | L  | L   | L   | Х  | Х  | Х         | ILLEGAL                              | 4    |

|                  | Н  | Х   | Х   | Х  | Х  | Х         | NOP→Row Active after trcd            |      |

|                  | L  | Н   | Н   | Н  | Х  | Х         | NOP→Row Active after trcd            |      |

| Row              | L  | Н   | Н   | L  | Х  | Х         | ILLEGAL                              |      |

| Activating       | L  | Н   | L   | Х  | BA | CA,A10/AP | ILLEGAL                              | 2    |

|                  | L  | L   | Н   | Н  | BA | RA        | ILLEGAL                              | 2    |

|                  | L  | L   | Н   | L  | BA | PA        | ILLEGAL                              | 2    |

|                  | L  | L   | L   | Х  | Х  | Х         | ILLEGAL                              | 2    |

|                  | Н  | Х   | Х   | Х  | Х  | Х         | NOP→Idle after trc                   |      |

|                  | L  | н   | Н   | Х  | Х  | Х         | NOP→Idle after trc                   |      |

| Refreshing       | L  | Н   | L   | Х  | Х  | Х         | ILLEGAL                              |      |

|                  | L  | L   | Н   | Х  | Х  | Х         | ILLEGAL                              |      |

|                  | L  | L   | L   | Х  | Х  | Х         | ILLEGAL                              |      |

#### Function Truth Table (Table 1, Continued)

Abbreviations

RA = Row Address NOP = No Operation Command BA = Bank Address CA = Column Address AP = Auto Precharge PA = Precharge All

Note: 1. All entries assume that CKE was active (High) during the preceding clock cycle and the current clock cycle.

- 2. Illegal to bank in specified state : Function may be legal in the bank indicated by BA, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 4. NOP to bank precharging or in idle state. May precharge bank indicated by BA (and PA).

- 5. Illegal if any banks is not idle.

#### Function Truth Table for CKE (Table 2)

| Current<br>State                   | CKE<br>n-1 | CKE<br>n | cs | RAS | CAS | WE | Address | Action                          | Note |

|------------------------------------|------------|----------|----|-----|-----|----|---------|---------------------------------|------|

| Self<br>Refresh                    | H          | X        | Х  | Х   | Х   | Х  | Х       | INVALID                         |      |

|                                    | L          | Н        | Н  | Х   | Х   | Х  | Х       | Exit Self Refresh→ABI after trc | 6    |

|                                    | L          | Н        | L  | Н   | Н   | Н  | Х       | Exit Self Refresh→ABI after trc | 6    |

|                                    | L          | Н        | L  | Н   | Н   | L  | Х       | ILLEGAL                         |      |

|                                    | L          | Н        | L  | Н   | L   | Х  | Х       | ILLEGAL                         |      |

|                                    | L          | Н        | L  | L   | Х   | Х  | Х       | ILLEGAL                         |      |

|                                    | L          | L        | Х  | Х   | Х   | Х  | Х       | NOP(Maintain Self Refresh)      |      |

| Both<br>Bank<br>Precharge<br>Power | Н          | Х        | Х  | Х   | Х   | Х  | Х       | INVALID                         |      |

|                                    | L          | Н        | Н  | Х   | Х   | Х  | Х       | Exit Power Down→ABI             | 7    |

|                                    | L          | Н        | L  | Н   | Н   | Н  | Х       | Exit Power Down→ABI             | 7    |

|                                    | L          | Н        | L  | Н   | Н   | L  | Х       | ILLEGAL                         |      |

| Down                               | L          | Н        | L  | Н   | L   | Х  | Х       | ILLEGAL                         |      |

|                                    | L          | Н        | L  | L   | Х   | Х  | Х       | ILLEGAL                         |      |

|                                    | L          | L        | Х  | Х   | Х   | Х  | Х       | NOP(Maintain Power Down Mode)   |      |

|                                    | Н          | Н        | Х  | Х   | Х   | Х  | Х       | Refer to Table 1                |      |

| All<br>Banks<br>Idle               | Н          | L        | Н  | Х   | Х   | Х  | Х       | Enter Power Down                | 8    |

|                                    | Н          | L        | L  | Н   | Н   | Н  | Х       | Enter Power Down                | 8    |

|                                    | Н          | L        | L  | Н   | Н   | L  | Х       | ILLEGAL                         |      |

|                                    | Н          | L        | L  | Н   | L   | Х  | Х       | ILLEGAL                         |      |

|                                    | Н          | L        | L  | L   | Н   | Х  | Х       | ILLEGAL                         |      |

|                                    | Н          | L        | L  | L   | L   | Н  | Х       | Enter Self Refresh              | 8    |

|                                    | Н          | L        | L  | L   | L   | L  | Х       | ILLEGAL                         |      |

|                                    | L          | L        | Х  | Х   | Х   | Х  | Х       | NOP                             |      |

| Any State                          | Н          | Н        | Х  | Х   | Х   | Х  | Х       | Refer to Operations in Table 1  |      |

| Other than<br>Listed<br>Above      | Н          | L        | Х  | Х   | Х   | Х  | Х       | Begin Clock Suspend next cycle  | 9    |

|                                    | L          | Н        | Х  | Х   | Х   | Х  | Х       | Exit Clock Suspend next cycle   | 9    |

| 7006                               | L          | L        | Х  | Х   | Х   | Х  | Х       | Maintain clock Suspend          |      |

Abbreviations : ABI = All Banks Idle

Note: 6. After CKE's low to high transition to exit self refresh mode. And a time of trc(min) has to be elapse after CKE's low to high transition to issue a new command.

7. CKE low to high transition is asynchronous as if restarts internal clock.

A minimum setup time "tSS + one clock" must be satisfied before any command other than exit.

- 8. Power-down and self refresh can be entered only from the all banks idle state.

- 9. Must be a legal command.

# \* Optional

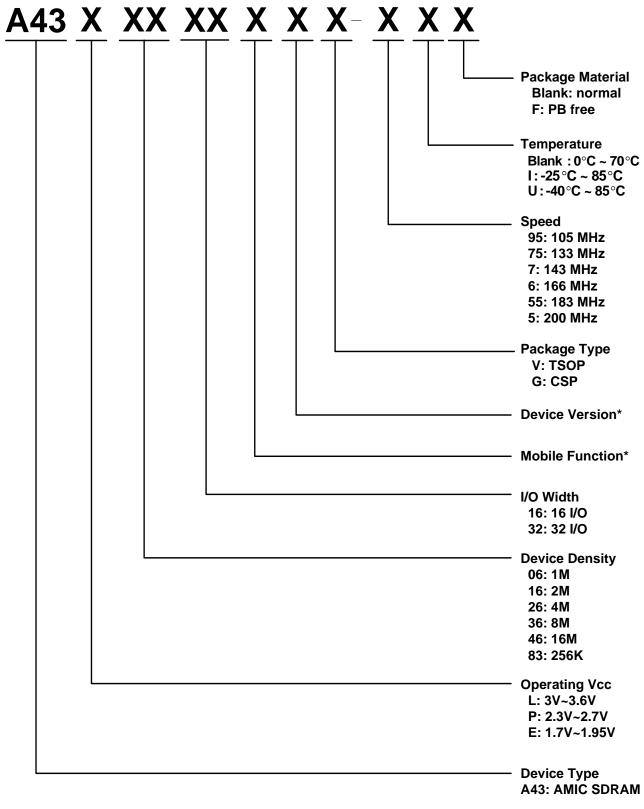

# **Ordering Information**

| Part No.        | Min. Cycle Time<br>(ns) | Max. Clock Frequency<br>(MHz) | Access Time | Package             |  |

|-----------------|-------------------------|-------------------------------|-------------|---------------------|--|

| A43E16321G-75F  | 7.5                     | 133                           | 6 ns        | 90 ball Pb-Free CSP |  |

| A43E16321G-75UF | 7.5                     | 133                           | 6 ns        | 90 ball Pb-Free CSP |  |

| A43E16321G-95F  | 9.5                     | 105                           | 7 ns        | 90 ball Pb-Free CSP |  |