# MCS9990 PCIe to 4-Port USB 2.0 Host Controller Datasheet

Revision 2.03 Nov. 25<sup>th</sup>, 2011

1

#### **IMPORTANT NOTICE**

Copyright © 2009-2011 ASIX Electronics Corporation. All rights reserved.

#### DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "reserved", "undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

#### TRADEMARKS

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

## Notation

The following conventions are used in this document

- A word is 16 bits wide

- A double word or Dword is 32 bits wide

- [x] Denotes the bit position in the register. [0] bit is the least significant position

- Base 16 numbers are denoted with a lowercase 'h' following a number or with a '0x' preceding a number

- Base 10 numbers are denoted with the absence of the above notation

- PU is pull-up on I/O pad

- PD is pull-down on I/O pad

- DS is Drive Strength in milli Amperes (mA)

- N/A is Not Applicable

- PROG is Programmable

- I is Input

- O is Output

- P is Passive

- "\_N" means the Signal is active low signal

- RSVD Reserved

The registers follow the following notation for the read and write access

| Name | Description            |

|------|------------------------|

| RO   | Read Only              |

| RW   | Read Write             |

| RWC  | Read/Write 1 to clear  |

| RW1  | Read or Write 1 to set |

| WO   | Write Only             |

| RC   | Read on clear          |

# Table of Contents

| 1. INTF | RODUCTION                                                                            | 6  |

|---------|--------------------------------------------------------------------------------------|----|

| 1.1     | GENERAL DESCRIPTION                                                                  | 6  |

| 1.2     | FEATURES                                                                             | 6  |

| 1.3     | APPLICATIONS                                                                         | 7  |

| 1.4     | BLOCK DIAGRAM                                                                        | 7  |

| 1.5     | PIN CONFIGURATION                                                                    | 8  |

| 1.6     | SUPPORT                                                                              |    |

| 1.7     | ORDERING INFORMATION                                                                 |    |

| 2. ARC  | HITECTURAL OVERVIEW                                                                  |    |

| 3. PIN  | DESCRIPTION                                                                          |    |

| 3.1     | PCI EXPRESS INTERFACE SIGNALS                                                        |    |

| 3.2     | USB INTERFACE SIGNALS                                                                | 14 |

| 3.2.1   | Port 0                                                                               | 14 |

| 3.2.2   | Port 1                                                                               | 14 |

| 3.2.3   | Port 2                                                                               | 15 |

| 3.2.4   |                                                                                      |    |

| 3.3     | ISA/GPIO INTERFACE SIGNALS DESCRIPTION                                               |    |

| 3.4     | I2C INTERFACE SIGNALS                                                                |    |

| 3.5     | MISC SIGNALS                                                                         |    |

| 3.6     | JTAG SIGNALS                                                                         |    |

| 3.7     | INTERNAL REGULATOR SIGNALS                                                           |    |

| 3.8     | POWER SIGNALS                                                                        | 19 |

| 3.9     | GROUND SIGNALS                                                                       | 20 |

| 4. MOI  | DE SELECTION AND FUNCTION MAPPING                                                    | 22 |

| 5. BOO  | ITSTRAP OPTIONS                                                                      |    |

|         | ISTER INFORMATION                                                                    |    |

| 6.1     | PCIE CONFIGURATION SPACE                                                             | 24 |

| 6.1.1   |                                                                                      |    |

| 6.1.2   | PCIe Configuration Space for OHCI Controller 2, 3, and 4 - (Function 2, 4 and 6)     | 25 |

| 6.1.3   | PCI Configuration Space for EHCI Controller 1, 2, 3 and 4 - (Function 1, 3, 5 and 7) | 26 |

| 6.2     | CONFIGURATION REGISTER SET                                                           |    |

| 6.2.1   | 1 8 8                                                                                |    |

| 6.3     | OHCI REGISTER SET                                                                    | 54 |

| 6.3.1   | Description of OHCI Operational Registers                                            |    |

| 6.4     | EHCI REGISTER SET                                                                    |    |

| 6.4.1   |                                                                                      |    |

| 6.5     | OTG REGISTER SET                                                                     |    |

| 6.5.1   |                                                                                      |    |

| 6.6     | GPIO REGISTER SET                                                                    |    |

| 6.7     | ISA REGISTER SET                                                                     |    |

| 6.7.1   |                                                                                      |    |

| 6.8     | EEPROM ACCESS REGISTER SET                                                           |    |

| 6.8.1   |                                                                                      |    |

| 6.9     | MISCELLANEOUS REGISTER SET                                                           |    |

# ASIX PCIe to 4-Port USB 2.0 Host Controller **MCS9990**

| 6.     | .9.1    | Description of Misc Registers                    | 118 |

|--------|---------|--------------------------------------------------|-----|

| 7. C   | LOCKS   | AND RESETS                                       | 127 |

| 8. E   | EPRON   | / CONTENT LAYOUT                                 | 128 |

| 9. P   | OWER    | MANAGEMENT                                       |     |

| 10.    | ELEC    | TRICAL SPECIFICATIONS                            |     |

| 10.1   | AB      | SOLUTE MAXIMUM RATINGS                           | 141 |

| 10.2   | 2 RE    | COMMENDED OPERATING CONDITIONS                   | 142 |

| 10.3   | B PO    | WER CONSUMPTION                                  | 143 |

| 10.4   | PC      | I EXPRESS PHY ELECTRICAL SPECIFICATIONS          | 144 |

| 10     | 0.4.1   | Electrical Characteristics                       | 144 |

| 10     | 0.4.2   | Static Characteristics: Digital Pins             | 144 |

| 10     | 0.4.3   | Static Characteristics: Analog I/O Pins          |     |

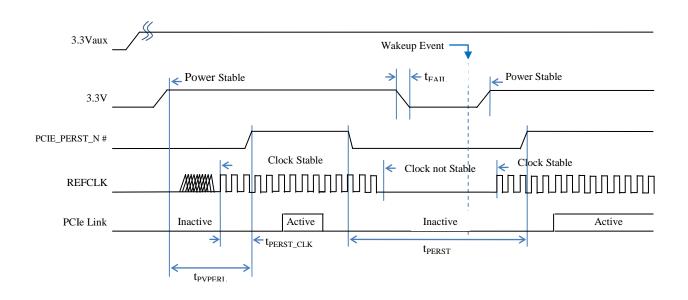

| 10     | 0.4.4   | Auxiliary Signal Timing (power up & reset)       |     |

| 10.5   | 5 US    | B PHY ELECTRICAL SPECIFICATIONS                  | 148 |

| 10     | 0.5.1   | Electrical Characteristics                       | 148 |

| 10     | 0.5.2   | Static Characteristics: Digital Pins             |     |

| 10     | 0.5.3   | Static Characteristics: Analog I/O Pins (DP/DM)  |     |

| 1(     | 0.5.4   | Dynamic Characteristics: Analog I/O Pins (DP/DM) | 151 |

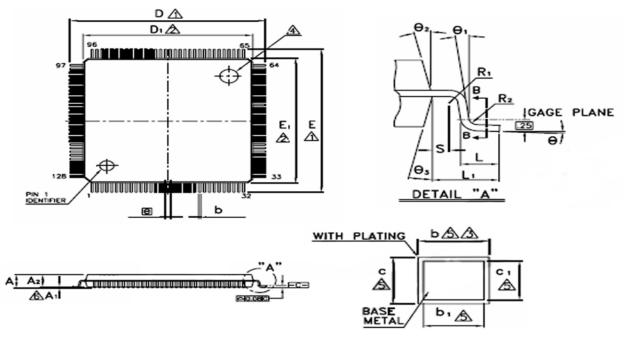

| 11.    | MECH    | HANICAL DIMENSIONS                               | 154 |

| REVISI | ION HIS | STORY                                            | 155 |

## 1. Introduction

## **1.1 General description**

MCS9990 is a single lane multi function PCI Express to USB2.0 Host Controller. It supports two modes of operation – USB Host mode and OTG mode, selectable through device mode select pins. The USB Host mode supports four USB2.0 Host ports. The OTG mode supports two USB2.0 Host ports, one USB OTG port and provision to select GPIO or ISA interface. The four USB2.0 host ports are integrated with on-chip transceivers and supports Enhanced Host Controller Interface (EHCI) and Open Host Controller Interface (OHCI). The USB OTG port is integrated with OTG PHY and supports host and device operations. The provisional ISA interface supports up to four serial ports and/or up to two parallel ports. The provisional 24 GPIO pins are programmable as an input or output.

## **1.2 Features**

### PCI Express

- Single-lane (x1) PCI Express endpoint controller with integrated PHY

- Compliant with PCI Express base specification revision 1.1

- Compliant with PCI Express Card specifications

- Supports multiple DMA transactions

- Supports eight PCI Express functions

- Supports Message TLP (error) generation

- Supports both legacy and MSI Interrupt mechanism

- Supports PCIe Power Management with ASPM support

### USB

- Four USB 2.0 Host Ports with on-chip transceivers, can handle High-speed (480Mbps), Full-speed (12Mbps) and low-speed (1.5Mbps) transactions

- One of the USB 2.0 Host Port can support OTG Feature

- Dedicated Enhanced Host Controller Interface (EHCI) controller per each port

- Dedicated Companion Open Host Controller Interface (OHCI) controller per each port

- Compatible with Bulk, Interrupt and Isochronous type USB devices

- Simultaneous operation of multiple high-performance devices

- Supports USB Power Management

- As a peripheral, OTG supports High Speed (HS)/ Full Speed (FS) Operation

- As a peripheral, OTG supports the following endpoints

- o One control endpoint

- One interrupt IN endpoint

- o Two Bulk IN endpoints

- o Two Bulk OUT endpoints

#### General Device Features

- Device parameters configurable through EEPROM

- 24 GPIO lines

- Optionally GPIO lines are configurable to support ISA Interface

- JTAG Port for board level diagnostics

- Power Supply requirement : 1.2V for Core & 3.3V for IO's

- On-chip Voltage regulator for 3.3V to 1.2V

## **1.3 Applications**

- Extend the USB ports on a PC

- Embedded applications for providing multiple USB ports

- Add-on I/O cards for serial port and parallel port through ISA interface

- PC/Server motherboard applications

- Digital Audio/Video applications

- NAS, Printer servers

- Video security monitoring applications

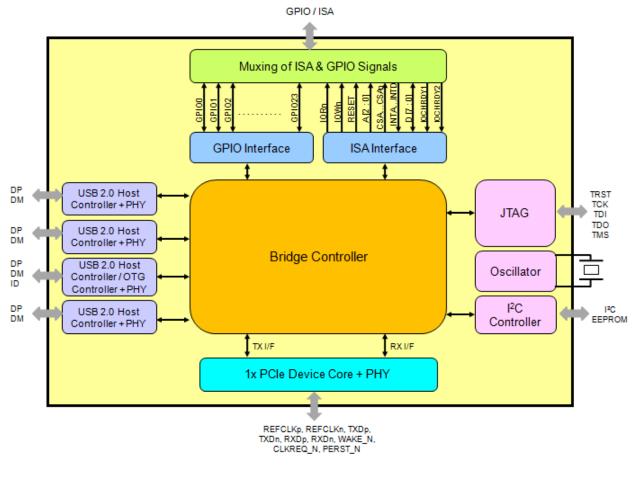

## 1.4 Block Diagram

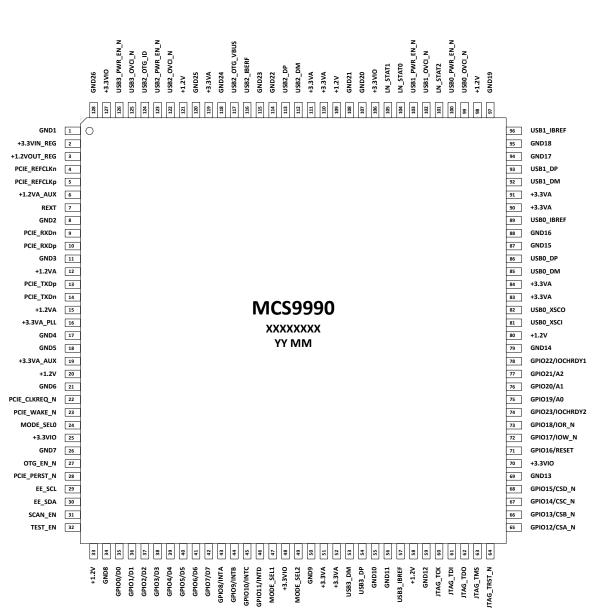

## 1.5 Pin Configuration

• 128-Pin LQFP (14x14)

Top View

# MCS9990 PCIe to 4-Port USB 2.0 Host Controller

| Pin# | Pin Name      | Pin# | Pin Name    | Pin# | Pin Name        | Pin# | Pin Name      |

|------|---------------|------|-------------|------|-----------------|------|---------------|

| 1    | GND1          | 33   | +1.2V       | 65   | GPIO12/CSA_N    | 97   | GND19         |

| 2    | +3.3VIN_REG   | 34   | GND8        | 66   | GPIO13/CSB_N    | 98   | +1.2V         |

| 3    | +1.2VOUT_REG  | 35   | GPIO0/D0    | 67   | GPIO14/CSC_N    | 99   | USB0_OVCI_N   |

| 4    | PCIE_REFCLKn  | 36   | GPIO1/D1    | 68   | GPIO15/CSD_N    | 100  | USB0_PWR_EN_N |

| 5    | PCIE_REFCLKp  | 37   | GPIO2/D2    | 69   | GND13           | 101  | LN_STAT2      |

| 6    | +1.2VA_AUX    | 38   | GPIO3/D3    | 70   | +3.3VIO         | 102  | USB1_OVCI_N   |

| 7    | REXT          | 39   | GPIO4/D4    | 71   | GPIO16/RESET    | 103  | USB1_PWR_EN_N |

| 8    | GND2          | 40   | GPIO5/D5    | 72   | GPIO17/IOW_N    | 104  | LN_STAT0      |

| 9    | PCIE_RXDn     | 41   | GPIO6/D6    | 73   | GPIO18/IOR_N    | 105  | LN_STAT1      |

| 10   | PCIE_RXDp     | 42   | GPIO7/D7    | 74   | GPIO23/IOCHRDY2 | 106  | +3.3VIO       |

| 11   | GND3          | 43   | GPIO8/INTA  | 75   | GPIO19/A0       | 107  | GND20         |

| 12   | +1.2VA        | 44   | GPIO9/INTB  | 76   | GPIO20/A1       | 108  | GND21         |

| 13   | PCIE_TXDp     | 45   | GPIO10/INTC | 77   | GPIO21/A2       | 109  | +1.2V         |

| 14   | PCIE_TXDn     | 46   | GPIO11/INTD | 78   | GPIO22/IOCHRDY1 | 110  | +3.3VA        |

| 15   | +1.2VA        | 47   | MODE_SEL1   | 79   | GND14           | 111  | +3.3VA        |

| 16   | +3.3VA_PLL    | 48   | +3.3VIO     | 80   | +1.2V           | 112  | USB2_DM       |

| 17   | GND4          | 49   | MODE_SEL2   | 81   | USB0_XSCI       | 113  | USB2_DP       |

| 18   | GND5          | 50   | GND9        | 82   | USB0_XSCO       | 114  | GND22         |

| 19   | +3.3VA_AUX    | 51   | +3.3VA      | 83   | +3.3VA          | 115  | GND23         |

| 20   | +1.2V         | 52   | +3.3VA      | 84   | +3.3VA          | 116  | USB2_IBERF    |

| 21   | GND6          | 53   | USB3_DM     | 85   | USB0_DM         | 117  | USB2_OTG_VBUS |

| 22   | PCIE_CLKREQ_N | 54   | USB3_DP     | 86   | USB0_DP         | 118  | GND24         |

| 23   | PCIE_WAKE_N   | 55   | GND10       | 87   | GND15           | 119  | +3.3VA        |

| 24   | MODE_SEL0     | 56   | GND11       | 88   | GND16           | 120  | GND25         |

| 25   | +3.3VIO       | 57   | USB3_IBREF  | 89   | USB0_IBREF      | 121  | +1.2V         |

| 26   | GND7          | 58   | +1.2V       | 90   | +3.3VA          | 122  | USB2_OVCI_N   |

| 27   | OTG_EN_N      | 59   | GND12       | 91   | +3.3VA          | 123  | USB2_PWR_EN_N |

| 28   | PCIE_PERST_N  | 60   | JTAG_TCK    | 92   | USB1_DM         | 124  | USB2_OTG_ID   |

| 29   | EE_SCL        | 61   | JTAG_TDI    | 93   | USB1_DP         | 125  | USB3_OVCI_N   |

| 30   | EE_SDA        | 62   | JTAG_TDO    | 94   | GND17           | 126  | USB3_PWR_EN_N |

| 31   | SCAN_EN       | 63   | JTAG_TMS    | 95   | GND18           | 127  | +3.3VIO       |

| 32   | TEST_EN       | 64   | JTAG_TRST_N | 96   | USB1_IBREF      | 128  | GND26         |

## 1.6 Support

| Reference Schematics                              | : Available***                 |

|---------------------------------------------------|--------------------------------|

| Evaluation Board                                  | : Available***                 |

| Software Support                                  | : Available***                 |

| System Design Data and Other Technical Collateral | : Available***                 |

| Certification                                     | : Already certified for PCIe   |

|                                                   | Compliance through FPGA System |

\*\*\* Please contact ASIX Support Team for above items, write to <a href="mailto:support@asix.com.tw">support@asix.com.tw</a>

## **1.7 Ordering Information**

| : MCS9990CV-AA   |

|------------------|

| : 0 to 85°C      |

| : 128 LQFP, RoHS |

|                  |

| : MCS9990IV-AA   |

| : -40 to 85°C    |

| : 128 LQFP, RoHS |

|                  |

## 2. Architectural Overview

MCS9990 is integrated host controller with USB 2.0 transceivers and PCIe interface in to a single chip. It consists of 4 OHCI, 4 EHCI, OTG, ISA, GPIO and I2C cores. MCS9990 compiles with USB specification revision 2.0 and OHCI Interface specification 1.0a for full-/low-speed signaling and Intel's EHCI specification 1.0 for high-speed signaling. MCS9990 contains PCIe PHY compliant with 1.1 PCIe end point controller, 4-port USB and OTG controller and a bridge that controls the transfers between the USB controller and the PCIe interface. In addition, MCS9990 supports an optional ISA interface, I2C, JTAG interface for board testability.

## PCIe PHY

This block is a Single-lane transceivers complaint with the PCIe base specification 1.1 and contains the high speed 2.5Gbps differential transmit and receive lines. This block performs the 8b/10b encoding and decoding, power management etc.

## PCIe Endpoint Controller

A PCIe endpoint controller is a device, which is similar to PCI/PCI-X based Host Bus Adapters. A root port needs to establish the linkup, initiate credits and then enumerate the endpoint before the endpoint starts any memory write/read cycles. This PCIe endpoint is fully compliant with PCIe base specification 1.1

PCIe architecture is specified in layers. It is classified into three layers namely transaction layer, data link layer, and physical layer. PCIe configuration uses standard mechanisms as defined in the PCI plug-and-play specification. The software layers will generate read and write requests that are transported by the transaction layer to the I/O devices using a packet-based, split-transaction protocol. The link layer adds sequence numbers and CRC to these packets to create a highly reliable data transfer mechanism. The basic physical layer consists of a dual-simplex channel that is implemented as a transmit pair and a receive pair. The link speed of 2.5Gbps/direction provides a 200MBps communication channel that is close to twice the classic PCI data rate.

### **Bridge Controller**

The bridge implements application master and application slave functional modules which take care of transmit and receive PCIe TLPs (Transaction Layer Packets).

Application master interacts with the transmit channels of the PCIe core and the USB host controller core. The data received on the USB interface are packetized by the application master interface as PCIe TLPs and supplied to the PCIe core for transmitting the data onto PCIe lines. The application slave interacts with receive as well as transmit channels of the PCIe core. It takes care of the TLPs received from the PCIe core and redirecting them to appropriate USB port. Also takes care of the completion packets onto PCIe lines using the transmit channel for the PCIe core.

#### USB 2.0 Host Controller

MCS9990 supports up to 4 USB 2.0 ports and each port can be configured independently and all ports operate simultaneously without any performance limitations. Under the USB Host mode, all 4 USB port are available and implements host controller ports. In OTG mode, in addition to an OTG port, 2 additional host controller ports are available.

#### **USB OTG Controller**

The OTG controller is compliant with USB Specification Rev 2.0 and OTG supplement Rev 1.0a. The host controller supports high (480 Mbps), full (12 Mbps) and low (1.5 Mbps) speed modes of operation. The device controller has two BULK IN and two BULK OUT endpoints, one Control and one Interrupt IN endpoint. The OTG controller supports both host negotiation protocol (HNP) and session request protocol (SRP). HNP is used to transfer control of a connection from the default Host (A-device) to the default peripheral (B-device). The OTG supplement defines two methods that are used by the B-device to request that the A-device to begin a session. They are called "Data-Line Pulsing" and "VBUS pulsing". These two methods comprise the Session request Protocol (SRP).

#### ISA Bridge

The ISA interface allows expanding the peripheral IOs, such as UARTs, parallel ports through external ISA interface components. ISA interface can be configured to support both 16 (Intel) mode and 68 (Motorola) Mode Data Bus Interface.

- Configured to support up to 4 UARTs

- Configured to supports parallel port interface

- ISA Interface can support following IO Configurations

- o 1 to 4 UARTs or 1 to 2 UARTs + 1 Parallel Port

When ISA Mode is selected, MCS9990 assumes the presence of an external "ISA to 4 Serial" peripheral configuration on the ISA interface, for default mode. For other ISA based Serial/Parallel combinations external EEPROM has to be used.

### **GPIO Interface**

The MCS9990 supports up to 24 General Purpose I/O (GPIO) pins to be used for system control and connection to various devices. Each GPIO pin can be programmed as an input or output and can also be used as interrupt request lines when programmed to input mode. The GPIO's can be configured as open drain signals in O/P mode. Has programmable internal pull-up capability.

### I2C Interface

The MCS9990 supports a 2-wire I2C interface for accessing an external EEPROM that supports both read and write operations. On power-up reset the EEPROM controller checks for the EEPROM presence. If EEPROM is present, controller loads the configuration data from the EEPROM and replaces the corresponding default values. The I2C interface has two signals – Serial Data (SDA) and Serial Clock (SCL) & supports 16-bit addressing with frequency rate up to 400 KHz.

# 3. Pin Description

## 3.1 PCI Express Interface Signals

| Pin# | Pin Name      | I/O/P | Туре   | DS | PU/PD | Description                                                                                                                                                             |

|------|---------------|-------|--------|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | PCIE_REFCLKn  | I     | LVDS   |    |       | PCIe differential clock<br>Negative                                                                                                                                     |

| 5    | PCIE_REFCLKp  | I     | LVDS   |    |       | PCIe differential clock<br>Positive                                                                                                                                     |

| 7    | REXT          | 0     | Analog |    |       | Band gap external<br>resistor, connect resistor<br>to Ground                                                                                                            |

| 9    | PCIE_RXDn     | I     | LVDS   |    |       | PCIe differential data<br>Receive Negative                                                                                                                              |

| 10   | PCIE_RXDp     | I     | LVDS   |    |       | PCIe differential data<br>Receive Positive                                                                                                                              |

| 13   | PCIE_TXDp     | 0     | LVDS   |    |       | PCIe differential data<br>Transmit Positive                                                                                                                             |

| 14   | PCIE_TXDn     | 0     | LVDS   |    |       | PCIe differential data<br>Transmit Negative                                                                                                                             |

| 22   | PCIE_CLKREQ_N | 0     | LVTTL  | 4  | PU    | Active low signal to<br>enable/disable the<br>reference clock of PCIe<br>card. When High,<br>Reference clock is<br>disabled.                                            |

| 23   | PCIE_WAKE_N   | 0     | LVTTL  | 4  | PU    | Wakeup, Active low<br>signal to request the host<br>platform to return from a<br>sleep/suspended state to<br>service a PCI express<br>function initiated wake<br>event. |

| 28   | PCIE_PERST_N  | I     | LVTTL  |    | PU    | Fundamental reset from<br>the PCIe connector.<br>Active Low                                                                                                             |

## **3.2** USB Interface Signals

#### 3.2.1 Port 0

USB Host Mode – Port will be USB 2.0 Host Port OTG Mode – Port will be USB 2.0 Host Port

| Pin# | Pin Name      | I/O/P | Туре   | DS | PU/PD | Description                                                                  |

|------|---------------|-------|--------|----|-------|------------------------------------------------------------------------------|

| 81   | USB0_XSCI     | I     | Analog |    |       | Crystal Oscillator Input –<br>12MHz                                          |

| 82   | USB0_XSCO     | 0     | Analog |    |       | Crystal Oscillator Output                                                    |

| 85   | USB0_DM       | I/O   | Analog |    |       | USB2.0 differential data negative                                            |

| 86   | USBO_DP       | I/O   | Analog |    |       | USB2.0 differential data positive                                            |

| 89   | USB0_IBREF    | I     | Analog |    |       | External reference<br>resistor (12.1 ΩK 1%)<br>connect resistor to<br>Ground |

| 99   | USB0_OVCI_N   | I     | LVTTL  |    | PU    | USB Over Current<br>Indication                                               |

| 100  | USB0_PWR_EN_N | 0     | LVTTL  | 4  |       | USB power enable signal                                                      |

All the four USB Ports will be sharing the USB0\_XSCI and USB0\_XSCO.

### 3.2.2 Port 1

USB Host Mode – Port will be USB 2.0 Host Port OTG Mode – Port will be USB 2.0 Host Port

| Pin# | Pin Name      | I/O/P | Туре   | DS | PU/PD | Description                                                                          |

|------|---------------|-------|--------|----|-------|--------------------------------------------------------------------------------------|

| 92   | USB1_DM       | I/O   | Analog |    |       | USB2.0 differential data negative                                                    |

| 93   | USB1_DP       | I/O   | Analog |    |       | USB2.0 differential data positive                                                    |

| 96   | USB1_IBREF    | I     | Analog |    |       | External reference<br>resistor (12. <b>f</b> X, 1%)<br>connect resistor to<br>Ground |

| 102  | USB1_OVCI_N   | I     | LVTTL  |    | PU    | USB Over Current<br>Indication                                                       |

| 103  | USB1_PWR_EN_N | 0     | LVTTL  | 4  |       | USB power enable signal                                                              |

#### 3.2.3 Port 2

USB Host Mode – Port will be USB 2.0 Host Port OTG Mode – Port will be USB OTG Port

| Pin# | Pin Name      | I/O/P | Туре   | DS | PU/PD | Description                                                                          |

|------|---------------|-------|--------|----|-------|--------------------------------------------------------------------------------------|

| 112  | USB2_DM       | I/O   | Analog |    |       | USB2.0 differential data negative                                                    |

| 113  | USB2_DP       | I/O   | Analog |    |       | USB2.0 differential data positive                                                    |

| 116  | USB2_IBREF    | I     | Analog |    |       | External reference<br>resistor (12. <b>D</b> /, 1%)<br>connect resistor to<br>Ground |

| 122  | USB2_OVCI_N   | I     | LVTTL  |    | PU    | USB Over Current<br>Indication                                                       |

| 123  | USB2_PWR_EN_N | О     | LVTTL  | 4  |       | USB power enable signal                                                              |

| 124  | USB2_OTG_ID   | I     | LVTTL  |    | PROG  | Identification pin for OTG<br>ports which differentiates<br>A-Device or B-Device     |

| 117  | USB2_OTG_VBUS | I     | LVTTL  |    |       | Voltage detection circuit input                                                      |

#### 3.2.4 Port 3

USB Host Mode – Port will be USB 2.0 Host Port OTG Mode – Port will not be available

| Pin# | Pin Name      | I/O/P | Туре   | DS | PU/PD | Description                                                                |

|------|---------------|-------|--------|----|-------|----------------------------------------------------------------------------|

| 53   | USB3_DM       | I/O   | Analog |    |       | USB2.0 differential data negative                                          |

| 54   | USB3_DP       | I/O   | Analog |    |       | USB2.0 differential data positive                                          |

| 57   | USB3_IBREF    | I     | Analog |    |       | External reference<br>resistor (12.0% 1%)<br>connect resistor to<br>Ground |

| 125  | USB3_OVCI_N   | I     | LVTTL  |    | PU    | USB Over Current<br>Indication                                             |

| 126  | USB3_PWR_EN_N | 0     | LVTTL  | 4  |       | USB Power Enable Signal                                                    |

## 3.3 ISA/GPIO Interface Signals Description

GPIO and ISA pins are multiplexed. These can be used with combination of OTG and 2 USB Host ports. ISA pins are available in **2USB+OTG+ISA** Mode and GPIO pins in **2USB+OTG+GPIO** Mode.

| Pin# | Pin Name | I/O/P | Туре  | DS | PU/PD | Description                                                   |

|------|----------|-------|-------|----|-------|---------------------------------------------------------------|

| 35   | D0       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 36   | D1       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 37   | D2       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 38   | D3       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 39   | D4       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 40   | D5       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 41   | D6       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 42   | D7       | I/O   | LVTTL | 4  | PD    | Data bus signal at ISA interface                              |

| 43   | INTA     | I     | LVTTL | 4  | PU/PD | Interrupt signal coming from<br>Port-A of external peripheral |

| 44   | INTB     | I     | LVTTL | 4  | PU/PD | Interrupt signal coming from<br>Port-B of external peripheral |

| 45   | INTC     | I     | LVTTL | 4  | PU/PD | Interrupt signal coming from<br>Port-C of external peripheral |

| 46   | INTD     | I     | LVTTL | 4  | PU/PD | Interrupt signal coming from<br>Port-D of external peripheral |

| 65   | CSA_N    | 0     | LVTTL | 4  |       | Chip Select line for Port-A of external peripheral            |

| 66   | CSB_N    | 0     | LVTTL | 4  |       | Chip Select line for Port-B of external peripheral            |

| 67   | CSC_N    | 0     | LVTTL | 4  |       | Chip Select line for Port-C of external peripheral            |

| 68   | CSD_N    | 0     | LVTTL | 4  |       | Chip Select line for Port-D of external peripheral            |

| 71   | RESET    | 0     | LVTTL | 4  |       | Reset signal for external peripheral at ISA interface         |

| 72   | IOW_N    | 0     | LVTTL | 4  |       | Write pulse for external peripheral at ISA interface          |

| 73   | IOR_N    | 0     | LVTTL | 4  |       | Read pulse for external peripheral at ISA interface           |

| 75   | A0       | 0     | LVTTL | 4  |       | External peripheral Address line                              |

| 76   | A1       | 0     | LVTTL | 4  |       | External peripheral Address line                              |

| 77   | A2       | 0     | LVTTL | 4  |       | External peripheral Address line                              |

| 78   | IOCHRDY1 | I     | LVTTL | 4  | PU    | IOCHRDY coming from Port-A of<br>external peripheral          |

| 74   | IOCHRDY2 | I     | LVTTL | 4  | PU    | IOCHRDY coming from Port-C of external peripheral             |

# MCS9990 PCIe to 4-Port USB 2.0 Host Controller

Note : In Intel mode (default Mode) pads are PD and in Motorola mode pads are PU.

#### **GPIO Interface Signals**

Available in 2USB+OTG+GPIO Mode Only

| Pin# | Pin Name | I/O/P | Туре  | DS | PU/PD | Description              |

|------|----------|-------|-------|----|-------|--------------------------|

| 35   | GPIO0    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 36   | GPIO1    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 37   | GPIO2    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 38   | GPIO3    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 39   | GPIO4    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 40   | GPIO5    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 41   | GPIO6    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 42   | GPIO7    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 43   | GPIO8    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 44   | GPIO9    | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 45   | GPIO10   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 46   | GPIO11   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 65   | GPIO12   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 66   | GPIO13   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 67   | GPIO14   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 68   | GPIO15   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 71   | GPIO16   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 72   | GPIO17   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 73   | GPIO18   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 75   | GPIO19   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 76   | GPIO20   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 77   | GPIO21   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 78   | GPIO22   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

| 74   | GPIO23   | I/O   | LVTTL | 4  | PROG  | General Purpose I/O Pins |

Note: 1. All the GPIO pins can be either PU or open and the PU's are Programmable. 2. All the GPIO/ISA pins should be made as NC's in the other device modes.

## 3.4 I2C Interface Signals

| Pin# | Pin Name | I/O/P | Туре  | DS | PU/PD | Description               |

|------|----------|-------|-------|----|-------|---------------------------|

| 29   | EE_SCL   | I/O   | LVTTL | 4  | PU    | 2-Wire EEPROM Clock       |

| 30   | EE_SDA   | I/O   | LVTTL | 4  | PU    | 2-Wire EEPROM Data In/Out |

## 3.5 Misc Signals

| Pin# | Pin Name  | I/O/P | Туре  | DS | PU/PD | Description                                                                                                                                                  |

|------|-----------|-------|-------|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27   | OTG_EN_N  | I     | LVTTL |    | PU    | Device Mode Select<br>$1 \rightarrow 4$ USB Host Controller mode<br>$0 \rightarrow 2$ USB Host Controller, 10TG<br>and ISA/GPIO mode                         |

| 24   | MODE_SEL0 | I     | LVTTL |    | PD    | Mode select line                                                                                                                                             |

| 47   | MODE_SEL1 | I     | LVTTL |    | PD    | Mode select line                                                                                                                                             |

| 49   | MODE_SEL2 | I     | LVTTL |    | PD    | Mode select line                                                                                                                                             |

| 31   | SCAN_EN   | I     | LVTTL |    | PD    | Scan Enable signal                                                                                                                                           |

| 32   | TEST_EN   | I     | LVTTL |    | PD    | Test Enable signal                                                                                                                                           |

| 104  | LN_STAT0  | I/O   | LVTTL | 4  |       | Active high status signal provides<br>information on link up of PCIe<br>interface. Also a Bootstrap Pin                                                      |

| 105  | LN_STAT1  | I/O   | LVTTL | 4  |       | Active high status signal provides<br>information on configuration of<br>PCIe functions on loading the<br>default / EEPROM contents. Also<br>a bootstrap Pin |

| 101  | LN_STAT2  | I/O   | LVTTL | 4  |       | Bootstrap pin. (Please refer to<br>"Bootstrap Options" section)                                                                                              |

## 3.6 JTAG Signals

JTAG interface can be used for board testability

| Pin# | Pin Name    | I/O/P | Туре  | DS | PU/PD                 | Description                 |

|------|-------------|-------|-------|----|-----------------------|-----------------------------|

| 60   | JTAG_TCK    | I     | LVTTL | -  |                       | JTAG chain clock            |

| 61   | JTAG_TDI    | I     | LVTTL |    | - PU JTAG chain input |                             |

| 62   | JTAG_TDO    | 0     | LVTTL | 4  |                       | JTAG chain output           |

| 63   | JTAG_TMS    | I     | LVTTL |    | PU                    | JTAG chain Test mode select |

| 64   | JTAG_TRST_N | I     | LVTTL |    | PU                    | Debug reset signal          |

## 3.7 Internal Regulator Signals

| Pin# | Pin Name     | I/O/P | Туре  | DS | PU/PD | Description                                       |

|------|--------------|-------|-------|----|-------|---------------------------------------------------|

| 2    | +3.3VIN_REG  | I     | Power |    |       | Power supply voltage for<br>Voltage Regulator PHY |

| 3    | +1.2VOUT_REG | 0     | Power |    |       | 1.2V output voltage                               |

## 3.8 Power Signals

| Pin# | Pin Name   | I/O/P | Туре  | DS | PU/PD | Description                                                   |

|------|------------|-------|-------|----|-------|---------------------------------------------------------------|

| 6    | +1.2VA_AUX | Р     | Power |    |       | 1.2V Analog auxiliary power for PCIe PHY                      |

| 19   | +3.3VA_AUX | Р     | Power |    |       | 3.3V Analog auxiliary power for PCIe PHY                      |

| 16   | +3.3VA_PLL | Р     | Power |    |       | 3.3V Analog Power Supply for<br>internal PLL used in PCIe PHY |

| 20   | +1.2V      | Р     | Power |    |       | 1.2V core power supply                                        |

| 33   | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 58   | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 80   | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 98   | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 109  | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 121  | +1.2V      | Р     | Power | -  |       | 1.2V core power supply                                        |

| 12   | +1.2VA     | Р     | Power | -  |       | 1.2V Analog/IO power supply                                   |

| 15   | +1.2VA     | Р     | Power | -  |       | 1.2V Analog/IO power supply                                   |

| 25   | +3.3VIO    | Р     | Power | -  |       | 3.3V Digital IO Power Supply                                  |

| 48   | +3.3VIO    | Р     | Power |    |       | 3.3V Digital IO Power Supply                                  |

| 70   | +3.3VIO    | Р     | Power |    |       | 3.3V Digital IO Power Supply                                  |

| 106  | +3.3VIO    | Р     | Power |    |       | 3.3V Digital IO Power Supply                                  |

# ASIX PCIe to 4-Port USB 2.0 Host Controller **MCS9990**

| Pin# | Pin Name | I/O/P | Туре  | DS | PU/PD | Description                                   |

|------|----------|-------|-------|----|-------|-----------------------------------------------|

| 127  | +3.3VIO  | Р     | Power |    |       | 3.3V Digital IO Power Supply                  |

| 51   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB3 PHY    |

| 52   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage for USB3 PHY       |

| 83   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB0 PHY    |

| 84   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB0 PHY    |

| 90   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB1 PHY    |

| 91   | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB1 PHY    |

| 110  | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB2 PHY    |

| 111  | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB2 PHY    |

| 119  | +3.3VA   | Р     | Power |    |       | 3.3V Analog supply voltage<br>for USB OTG PHY |

#### **Ground Signals** 3.9

| Pin# | Pin Name | I/O/P | Туре   | DS | PU/PD | Description |

|------|----------|-------|--------|----|-------|-------------|

| 1    | GND1     | Р     | Ground |    |       | Ground      |

| 8    | GND2     | Р     | Ground |    |       | Ground      |

| 11   | GND3     | Р     | Ground |    |       | Ground      |

| 17   | GND4     | Р     | Ground |    |       | Ground      |

| 18   | GND5     | Р     | Ground |    |       | Ground      |

| 21   | GND6     | Р     | Ground |    |       | Ground      |

| 26   | GND7     | Р     | Ground |    |       | Ground      |

| 34   | GND8     | Р     | Ground |    |       | Ground      |

| 50   | GND9     | Р     | Ground |    |       | Ground      |

Copyright © 2009-2011 ASIX Electronics Corporation. All rights reserved.

# **MCS9990** ASIX PCIe to 4-Port USB 2.0 Host Controller

| Pin#   | Pin Name   | I/O/P | Туре   | DS | PU/PD | Description |

|--------|------------|-------|--------|----|-------|-------------|

| 1 111# | T III Name | 1/0/1 | Type   | 05 | 10/10 | Description |

| 55     | GND10      | Р     | Ground |    |       | Ground      |

| 56     | GND11      | Р     | Ground |    |       | Ground      |

| 59     | GND12      | Р     | Ground |    |       | Ground      |

| 69     | GND13      | Р     | Ground |    |       | Ground      |

| 79     | GND14      | Р     | Ground |    |       | Ground      |

| 87     | GND15      | Р     | Ground |    |       | Ground      |

| 88     | GND16      | Р     | Ground |    |       | Ground      |

| 94     | GND17      | Р     | Ground |    |       | Ground      |

| 95     | GND18      | Р     | Ground |    |       | Ground      |

| 97     | GND19      | Р     | Ground |    |       | Ground      |

| 107    | GND20      | Р     | Ground |    |       | Ground      |

| 108    | GND21      | Р     | Ground |    |       | Ground      |

| 114    | GND22      | Р     | Ground |    |       | Ground      |

| 115    | GND23      | Р     | Ground |    |       | Ground      |

| 118    | GND24      | Р     | Ground |    |       | Ground      |

| 120    | GND25      | Р     | Ground |    |       | Ground      |

| 128    | GND26      | Р     | Ground |    |       | Ground      |

Note : All ground signal can be shorted at system level, refer to reference schematics for additional details.

## 4. Mode Selection and Function Mapping

### Mode Selection

MCS9990 supports following four functional modes, selectable through device mode select pins at board level.

| Mode Selection          | TEST_EN | MODE_SEL2 | MODE_SEL1 | MODE_SEL0 | OTG_EN_N |

|-------------------------|---------|-----------|-----------|-----------|----------|

| 4 USB Host              | 0       | 0         | 0         | 0         | 1        |

| 2 USB Host + OTG        | 0       | 0         | 0         | 1         | 0        |

| 2 USB Host + OTG + ISA  | 0       | 0         | 1         | 0         | 0        |

| 2 USB Host + OTG + GPIO | 0       | 0         | 1         | 1         | 0        |

#### **Function Mapping**

MCS9990 supports four functional modes. All these functional modes have different peripheral mapping with respect to the functions configured by PCIe. In all there are eight functions in all the four modes. Following table shows different function mapping in different functional modes.

| Function   | 4 Host USB   | 2 USB + OTG  | 2 USB + OTG + ISA | 2 USB + OTG + GPIO |

|------------|--------------|--------------|-------------------|--------------------|

| Function 0 | OHCI for CH0 | OHCI for CH0 | OHCI for CH0      | OHCI for CH0       |

| Function 1 | EHCI for CH0 | EHCI for CH0 | EHCI for CH0      | EHCI for CH0       |

| Function 2 | OHCI for CH1 | OHCI for CH1 | OHCI for CH1      | OHCI for CH1       |

| Function 3 | EHCI for CH1 | EHCI for CH1 | EHCI for CH1      | EHCI for CH1       |

| Function 4 | OHCI for CH2 | OHCI for CH2 | OHCI for CH2      | OHCI for CH2       |

| Function 5 | EHCI for CH2 | EHCI for CH2 | EHCI for CH2      | EHCI for CH2       |

| Function 6 | OHCI for CH3 | OTG for CH2  | OTG for CH2       | OTG for CH2        |

| Function 7 | EHCI for CH3 | NA           | ISA               | GPIO               |

# 5. Bootstrap Options

In MCS9990, six bootstrap options are present.

| Pin Name | Bootstrap        | Internal<br>PU/PD | Default<br>External<br>PU/PD | Description                                                                                                                                                                                                                              |

|----------|------------------|-------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LN_STATO | PCIEXP_ERR_MSK   | PD                | PU                           | To mask PCle error bits.<br>By default logic 'Low' is<br>present to mask error<br>reporting                                                                                                                                              |

| LN_STAT1 | MAXRD_128BYTES   | PD                | Open                         | To set maximum read<br>request size from EP to be<br>128 bytes by passing high<br>logic on the line. By<br>default logic 'Low' is<br>present                                                                                             |

| LN_STAT2 | AUX_POWER        | PD                | Open                         | For auxiliary power<br>detection, connected to<br>'Vaux' detect circuit at<br>board level. By default<br>logic 'Low' is present                                                                                                          |

| GPIO19   | ASPM_CNTRL       | PU                | Open                         | To Provide ASPM support<br>controllability. By default<br>logic 'High' is present to<br>enable ASPM                                                                                                                                      |

| GPIO20   | ADV_ERROR_REPORT | PU                | Open                         | To provide Advance Error<br>Report support<br>controllability. By default<br>logic 'High' is present to<br>enable the feature.                                                                                                           |

| GPIO21   | WAKE_HIB_EN      | PU                | Open                         | To provide wake from D3<br>Cold (Hibernate) state<br>through device connected<br>under USB host. By<br>default logic 'High' is<br>present to disable this<br>feature. To enable the<br>feature provide weak pull<br>down at board level. |

## 6. Register Information

## 6.1 PCIe Configuration Space

## 6.1.1 PCIe Configuration Space for OHCI Controller 1 - (Function 0)

|                   | 24 23 1<br>Device ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 15 8<br>Vend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7<br>dor ID                       |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| St                | tatus Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Comman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Command Register                  |  |

| Class Code        | Subclass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Revision ID                       |  |

| BIST              | Header Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Latency Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cache Line Size                   |  |

|                   | BAR_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OHCI Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ldress Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ldress Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ldress Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |  |