# CHT-OPAL PRELIMINARY DATASHEET

High-Temperature, Ultra High-Precision Dual Operational Amplifier

## **General description**

CHT-OPAL is an ultra high-precision, dual operational amplifier designed for applications that require very low offset and very low noise. Both amplifiers can be configured as a differential amplifier or as an instrumentation amplifier (combined with a third, external amplifier cell and with external resistors). Key features include single 5V nominal power supply and rail-to-rail inputs and outputs. Best-in-class precision on the full temperature range -55°C to +225°C encompass low input offset (internally compensated) and low noise. The internal circuitry uses a clock that is internally generated. There is a spread-spectrum mode for this clock. The user can decide not to use this internal clock and rather provide it from external circuitry (e.g. for synchronization purposes).

CHT-OPAL also features a Stand-by mode that disables the two Op Amps and place the circuit in a low power consumption mode when the function is not needed.

## Features

Junction operating temperature from -55°C to 225°C

Version: 1.4

- Single supply operation: 5V ±10%

- Low offset: 50μV typ, 100 μV max

- Low noise: 5 µVpp typ

- High CMRR: 85 dB min

- Product gain bandwidth: 2.8 MHz typ

- Stable for gains above 3 (with <50pF load) and 5 (with 50~200pF load)

- Slew rate: 2.7 V/µs typ

- Rail-2-rail input and output

- Low bias input current: <10 pA typ

- Quiescent current: 1.2 mA typ.

- Automatic offset compensation

- Stand-by current: 7 µA max

- Latch-up free

- Package: TDFP16

## Applications

- High temperature instrumentation & data acquisition

- Signal conditioning & instrumentation amplifiers for temperature, pressure, motion, speed and position sensors

- Strain gage amplifiers

- Photodiode and PMT amplifiers

- Charge amplifiers

- Current sensing

- Transmitters (4-20mA, etc.)

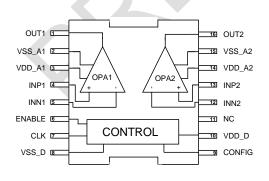

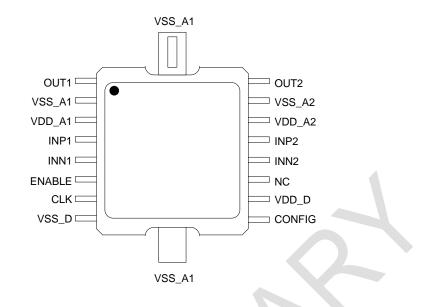

## Pinout

| Pin # | Pin Name            | Pin Description                      |  |  |

|-------|---------------------|--------------------------------------|--|--|

| 1     | OUT1                | Output OPA1                          |  |  |

| 2     | VSS_A1              | Negative power supply Analog OPA1    |  |  |

| 3     | VDD_A1              | Positive power supply Analog OPA1    |  |  |

| 4     | INP1                | Positive input pin OPA1              |  |  |

| 5     | INN1                | Negative input pin OPA1              |  |  |

| 6     | ENABLE              | Enable input pin <sup>1</sup>        |  |  |

| 7     | CLK                 | Input clock signal <sup>1</sup>      |  |  |

| 8     | VSS_D               | Negative power supply digital part   |  |  |

| 9     | CONFIG              | Configuration input pin <sup>1</sup> |  |  |

| 10    | VDD_D               | Positive power supply digital part   |  |  |

| 11    | NC                  | Not connected                        |  |  |

| 12    | INN2                | Negative input pin OPA2              |  |  |

| 13    | INP2                | Positive input pin OPA2              |  |  |

| 14    | VDD_A2              | Positive power supply Analog OPA2    |  |  |

| 15    | VSS_A2              | Negative power supply Analog OPA2    |  |  |

| 16    | 16 OUT2 Output OPA2 |                                      |  |  |

The 2 vertical large leads are internally connected to VSS\_A1 and are also connected to the package heat sink.

<sup>&</sup>lt;sup>1</sup> Cfr "Mode of operations" for details about function of pins "CLK", "CONFIG" and "ENABLE"

## **Absolute Maximum Ratings**

| $ \begin{array}{l} V_{DD\_x} - V_{SS\_x} \\ V_{SS\_x} - V_{SS\_Y} \\ V_{DD\_x} - V_{DD\_Y} \\ \end{array} \\ \hline \\ Voltage \ on \ any \ pin \ wrt \ to \ V_{SS\_x} \\ Junction \ Temperature \ (Tj) \end{array} $ | -0.5 to 6V<br>max 0.5V<br>max 0.5V<br>-0.5 to V <sub>DD_X</sub> +0.5V<br>250°C |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                                                                                                                                                                                                                       |                                                                                |

#### ESD Rating

Human Body Model

## **Operating Conditions**

| Supply Voltage V <sub>DD_X</sub> to V <sub>SS_X</sub> : |

|---------------------------------------------------------|

| Junction temperature                                    |

4.5V to 5.5V -55°C to +225°C

**CAUTION:** Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Frequent or extended exposure to absolute maximum rating conditions or above may affect device reliability. Permanent uses of the device in short-circuit state or in over-temperature state may affect long term reliability of the device.

>2KV

## **DC Electrical Characteristics**

Unless otherwise stated,  $T_j = 25^{\circ}$ C,  $V_{DD_D}/V_{DD_A1}/V_{DD_A2}=5$ V. **Bold** figures point out values valid over the whole temperature range ( $T_j = -55^{\circ}$ C to +225^{\circ}C).

| Parameter                         | Symbol                | Condition                                                     | Min  | Тур  | Max              | Unit |

|-----------------------------------|-----------------------|---------------------------------------------------------------|------|------|------------------|------|

| Supply Voltage                    | $V_{DD_X} - V_{SS_X}$ |                                                               | 4.5  | 5    | 5.5              | V    |

| Output voltage range              | V <sub>OUT</sub>      |                                                               | 0    |      | 5                | V    |

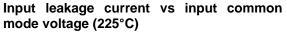

| Quiescent current                 | Ι <sub>Q</sub>        | CLK= '0'; CONFIG= '0'<br>1 amplifier active, no load          |      | 1.2  | 2                | mA   |

| Standby current                   | I <sub>STDBY</sub>    | CLK= '0'; CONFIG= '0',<br>ENABLE = '0'; T <sub>j</sub> = 25°C |      | 1.5  |                  | μA   |

|                                   | ISIDBY                | CLK= '0'; CONFIG= '0',<br>ENABLE = '0'; Tj = 225°C            |      |      | 7                | μA   |

| Internal clock frequency          | F <sub>INT</sub>      | CLK= '0'; CONFIG= '0';<br>T <sub>j</sub> = 25°C               |      | 360  |                  | kHz  |

|                                   |                       | RL=250Ω                                                       | 0.35 |      | VDD<br>-0.4      | V    |

| Output voltage swing              | Vo                    | RL=1kΩ                                                        | 0.09 |      | VDD<br>-0.1      | V    |

|                                   |                       | RL=∞                                                          | 0.01 |      | VDD<br>-<br>0.01 | V    |

| Max Output current <sup>1,2</sup> | 1                     | T <sub>j</sub> =25°C                                          | 20   |      |                  | mA   |

| Max Output current                | lo                    | T <sub>j</sub> =225°C                                         | 15   |      |                  | mA   |

| Output short-circuit current      | I <sub>SC</sub>       |                                                               |      | 100  |                  | mA   |

| External output capacitance       |                       |                                                               |      |      | 200              | pF   |

| Common mode input range           | V <sub>CM</sub>       |                                                               | 0.1  |      | VDD<br>-0.1      | V    |

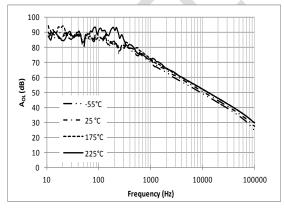

| Input offect veltere              |                       | T <sub>j</sub> =25°C                                          |      | 50   |                  | μV   |

| Input offset voltage              | VIOFF                 | T <sub>j</sub> =225°C                                         |      |      | 100              | μV   |

| Input offset drift                | TC <sub>VIOFF</sub>   | Maximum variation over [-<br>40-175]°C temperature<br>range   |      |      | 90               | μV   |

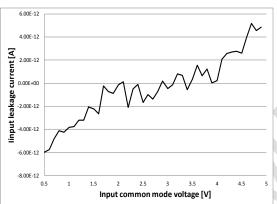

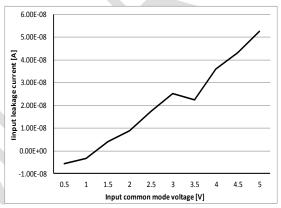

| Input lookogo ourront             |                       | T <sub>j</sub> =25°C, CMInput = 2.5V                          |      | ±7   |                  | pА   |

| Input leakage current             | I <sub>B</sub>        | T <sub>j</sub> =225°C, CMInput = 2.5V                         |      | ±50  |                  | nA   |

| hand all a summary                |                       | Tj=25°C                                                       |      | ±14  |                  | pА   |

| Input offset current              | I <sub>OFF</sub>      | T <sub>j</sub> =225°C                                         |      | ±120 |                  | nA   |

|                                   |                       | Differential,<br>CMInput = 2.5V                               |      | 1.5  |                  | pF   |

| Input capacitance                 | C <sub>IN,CM</sub>    | Single-ended,<br>CMInput = 2.5V                               |      | 3    |                  | pF   |

| Open-loop output impedance        |                       | lo=0mA, f=3MHz, Av=+1                                         | 150  | 250  | 400              | Ω    |

| Theread are state                 | θ <sub>JC</sub>       |                                                               |      | 11   |                  | °C/W |

| Thermal resistance                | θ <sub>JA</sub>       | pad area = $1 \text{ cm}^2$                                   |      | 80   |                  | °C/W |

<sup>&</sup>lt;sup>1</sup> Source or sink. <sup>2</sup> Output current is not internally limited. Value given indicates the maximum recommended conditions.

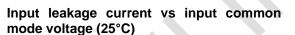

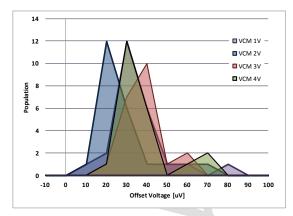

AC Electrical Characteristics Unless otherwise stated, T<sub>j</sub> = 25°C, V<sub>DD\_D</sub>/V<sub>DD\_A1</sub>/V<sub>DD\_A2</sub>=5V. Bold figures point out values valid over the whole temperature range (T<sub>j</sub> = -55°C to +225°C).

| Parameter                      | Symbol          | Condition                                                                     | Min | Тур  | Max | Unit         |  |

|--------------------------------|-----------------|-------------------------------------------------------------------------------|-----|------|-----|--------------|--|

| DC open-loop gain              |                 | RL= $2k\Omega$ , T <sub>j</sub> = $25^{\circ}$ C,<br>CMInput = $2.5$ V        |     | 85   |     | dB           |  |

| DC open-loop gain              | Ao              | RL= $2k\Omega$ , T <sub>j</sub> = $225^{\circ}C$<br>CMInput = $2.5V$          |     | 85   |     | dB           |  |

| Gain-bandwidth product         | GBW             | RL=2k $\Omega$ , CL=30pF, T <sub>j</sub> =25°C<br>CMInput = 2.5V              | 2.2 | 2.8  |     | MHz          |  |

| Gain-bandwidth product         | GBW             | RL=2k $\Omega$ , CL=30pF, T <sub>j</sub> =225°C<br>CMInput = 2.5V             | 2.5 | 3.6  |     | MHz          |  |

| Common mode rejection ratio    | CMRR            | DC to 1kHz, T <sub>j</sub> =25°C                                              | 85  | 105  | 4   | dB           |  |

| Common mode rejection ratio    | CIVIKK          | DC to 1kHz, T <sub>j</sub> =225°C                                             | 88  | 99   |     | dB           |  |

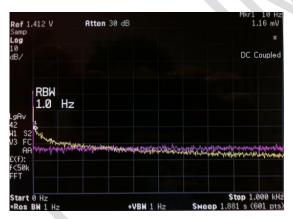

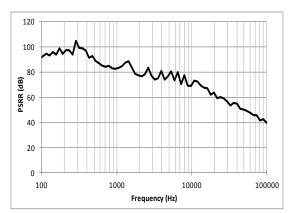

| Power supply rejection ratio   | PSRR            | Positive or negative.<br>DC to 100Hz, T <sub>j</sub> =25°C<br>CMInput = 2.5V  |     | 95   |     | dB           |  |

|                                |                 | Positive or negative.<br>DC to 100Hz, T <sub>j</sub> =225°C<br>CMInput = 2.5V |     | 95   |     | dB           |  |

| Slew rate                      | SR              | RL=2kΩ, CL=30pF, T <sub>j</sub> =25°C                                         | 1.9 | 2.7  |     | V/µs         |  |

| Slew fale                      | SR              | RL=2kΩ, CL=30pF, Tj=225°C                                                     | 3   | 4    |     |              |  |

|                                | $\Phi_{M}$      | RL=2kΩ, CL=30pF, T <sub>j</sub> =25°C                                         | 35  | 41   |     | 0            |  |

| Phase margin                   |                 | RL=2kΩ, CL=30pF, T <sub>j</sub> =225°C                                        | 27  | 32   |     | 0            |  |

|                                |                 | F=10Hz                                                                        |     | 0.3  |     | μV/√<br>Hz   |  |

|                                |                 | F=100Hz                                                                       |     | 0.3  |     |              |  |

| Input noise spectral density   | e <sub>sd</sub> | F=1kHz                                                                        |     | 0.3  |     |              |  |

|                                |                 | F=10kHz                                                                       |     | 0.09 |     |              |  |

| Integrated input noise voltage | e <sub>ni</sub> | 0.1 Hz to 10Hz                                                                |     | 5    |     | $\mu V_{pp}$ |  |

| Input noise current            |                 | 10Hz                                                                          |     | TBD  |     | fA/√H<br>z   |  |

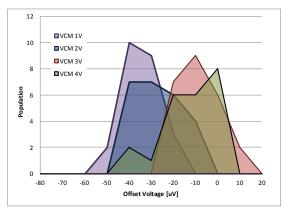

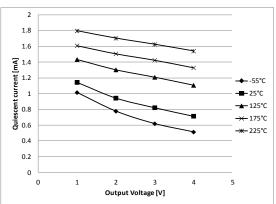

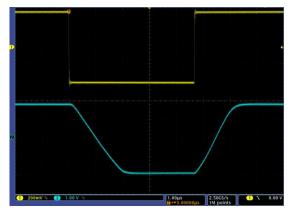

## **Typical Performance Characteristics**

Input Offset distribution (VDD=5V, T=25°C)

(VCM= Input common mode voltage)

Open loop Gain vs Frequency (no load)

Input Offset maximum thermal drift over [-40°C-175°C] temperature range (VDD=5V)

Supply current vs temperature

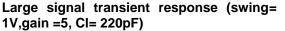

Small signal transient response (swing= 100mV,gain =5, CI= 220pF)

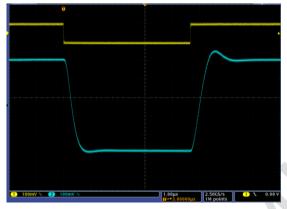

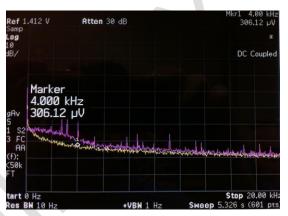

Voltage noise Density from 0.1Hz to 1 KHz (purple: with compensation; yellow: without compensation) (real value = measured value – 60dB)

**PSRR vs Frequency**

Voltage noise Density from 0.1Hz to 20 KHz (purple: with compensation; yellow: without compensation) (real value = measured value – 60dB)

### **Circuit Functionality**

#### Architecture

CHT-OPAL implements two low-noise, low-offset operational amplifier cells.

The amplifiers implement a proprietary compensation architecture for automatic offset correction and low-frequency noise improvement on the whole temperature range. As the use of a compensation clock generates unavoidable clock ripple on the output signal, and even though special care has been taken to the circuit design in order to minimize this ripple, the user may need to filter it externally. CHT-OPAL offers several configuration options in order to bring maximum flexibility to the user in regards to filtering: The clock operation can implement a spread spectrum function, which allows minimization of the output ripple amplitude on the clock frequency, the noise (ripple) energy being spread on the harmonics. Alternatively, the spread spectrum function can be disabled, in which case 100% of the ripple will be concentrated on the clock frequency. This later option is more suitable when external filtering (notch filter) or synchronization with external sampling devices is implemented.

Secondly, OPAL's offset compensation block can run either from an internal clock or from an external clock; the latter allows external synchronization and will typically be used by sampled systems (e.g. ADC). Use of the internal clock operation does not require any dedicated external components (e.g. capacitance). Selection of the external clock frequency can be made within a very wide range of 12 KHz to 500 KHz: the user will find an adequate frequency outside the useful bandwidth in most instrumentation and sensing applications.

When the spread spectrum function is enabled, CHT-OPAL compensation circuitry operates with a pseudo-random clock (generated from the master internal or external clock). This pseudo-random clock is generated by a 32-to-64 divider of the master clock (5.5 KHz to 11 KHz typ. When generated from the internal clock). This spreads the clock noise over a frequency octave.

CHT-OPAL also features a shutdown mode where the 2 Op Amps are inactive; the circuit is then in its lowest power consumption mode, with only a few  $\mu$ A drawn from the power supply.

#### External gain setting

CHT-OPAL should not be used in unitygain configuration. Minimum gain setting should be:

- 5 for output capacitance between 50 and 200 pF

- 3 for output capacitance below 50 pF.

#### Modes of operation

OPAL's behavior is controlled by 3 configuration pins. Table1 below summarizes the 5 different modes of operation.

| CLK        | CONFIG | ENABLE | MODE  | OPERATION                                   |

|------------|--------|--------|-------|---------------------------------------------|

| Х          | Х      | 0      | MODE1 | Standby mode                                |

| 0          | 0      | 1      | MODE2 | Internal oscillator;spreadspectrum enabled  |

| CLK > 9kHz | 0      | 1      | MODE3 | External clock;spreadspectrum enabled       |

| 1          | 0      | 1      |       | Internal test mode                          |

| 0          | 1      | 1      | MODE4 | Internal oscillator;spreadspectrum disabled |

| CLK > 9kHz | 1      | 1      | MODE5 | External clock;spreadspectrum disabled      |

| 1          | 1      | X      |       | Internal test mode                          |

#### MODE1:

By setting the pin ENABLE to "0", OPAL is put in standby mode where current consumption is reduced to a few  $\mu$ A.

#### MODE[2..5]:

Those 4 modes are standard modes of operation for OPAL. They differ by the way the internal auto-zero control signals are internally generated.

If CLK pin is put to "0", the master clock is generated by an internal oscillator (Fosc = 360 KHz typ.).

Whenever OPAL' internal circuitry senses an external clock signal with a frequency higher than 9KHz applied on the CLK pin, the circuits operates automatically in external clock mode, using CLK signal as the master clock.

With the CONFIG pin, one can configure OPAL to use the spread spectrum function to generate the internal auto-zero control signals

Choice of one of those 4 modes depends on the application constraints (signal useful band, synchronization with external devices...).

#### Single OPA

If the application only requires a single operational amplifier, the OPAL current consumption can be optimized by connecting VDD\_A1 or VDD\_A2 to respectively VSS\_A1 or VSS\_A2.

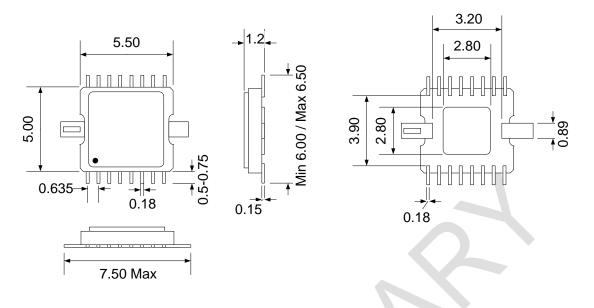

## Package Dimensions (TDFP16)

Physical dimensions (mm +/- 10%)

## **Ordering Information**

| Product Name | Ordering Reference    | Package | Marking      |

|--------------|-----------------------|---------|--------------|

| CHT-OPAL     | CHT-GEM6489A-TDFP16-T | TDFP16  | CHT-GEM6489A |

## **Contact & Ordering**

#### **CISSOID S.A.**

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium<br>T : +32 10 48 92 10 – F : +32 10 88 98 75<br>Email : <u>sales@cissoid.com</u> |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: <u>http://www.cissoid.com</u>                                                                                                    |

#### Disclaimer

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.

WWW.CISSOID.COM