# The Leader in High Temperature Semiconductor Solutions

# **CHT-THEMIS**

Version: 2.2 12-Nov-13 (Last Modification Date)

# **Power Transistor Driver Controller**

## **General description**

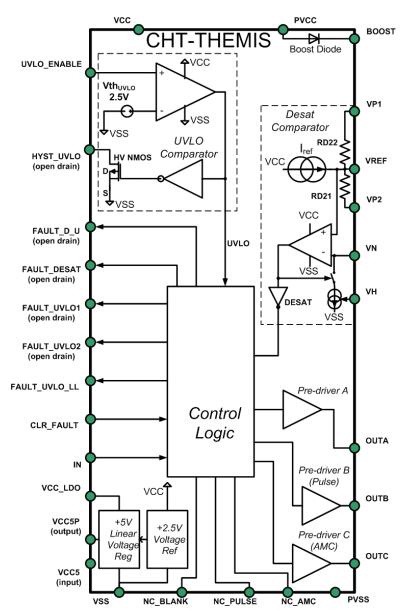

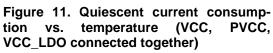

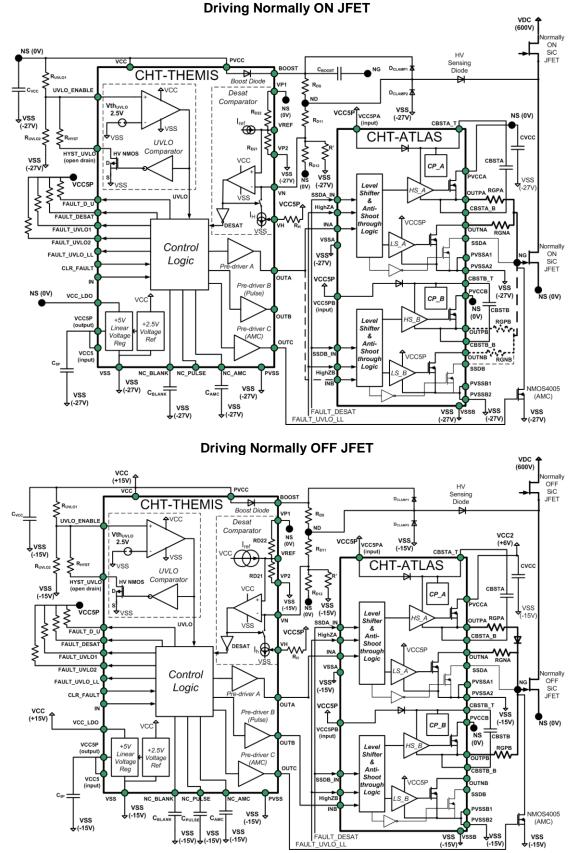

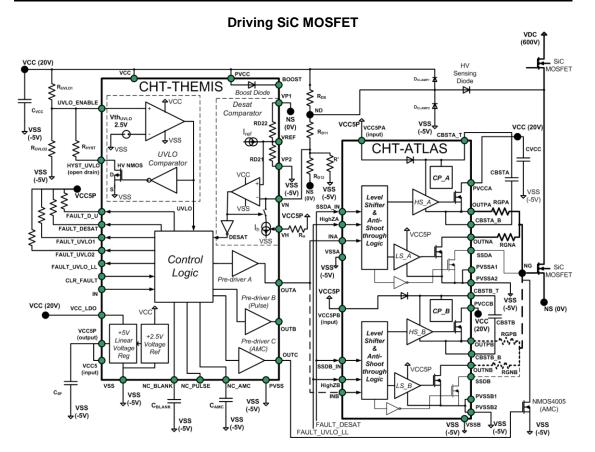

CHT-THEMIS is the controller block of the Power Transistor Driver solution CHT-THEMIS and CHT-ATLAS. The chipset is specifically designed to drive wide-bandgap power transistors, in particular Gallium Nitride (GaN) and Silicon Carbide (SiC) devices including normally-On and normally-Off JFETs, MOSFETs and BJTs. It is also used with standard silicon MOSFETs and IGBTs in standard temperature applications (e.g. 125°C) where it brings an increase in reliability and lifetime by an order of magnitude compared to traditional solutions. CHT-THEMIS can drive up to 5 CHT-ATLAS chips for very high power applications that require up to ±20A to the gate of the power device. It implements a state machine that manages the control and the fault signals, it embeds a voltage reference as well as a 5V linear voltage regulator which is used to supply CHT-ATLAS. This 5V power supply can also be used to power up other external circuits, such as the isolated transceiver CHT-RHEA for complete isolated gate-drive implementations. The circuit features an adjustable under-voltage lockout (UVLO) function with hysteresis as well as a de-saturation detection circuit. It also includes a pulse generation pre-driver to accommodate for Normally Off SiC JFET. CHT-THEMIS also features an active Miller clamping (AMC) function and predriver for an external transistor.

#### Features

- Operating junction temperature: from -55°C to +225°C

- Supply Voltage: 5 to 30V

- Adjustable Under-voltage lockout (UVLO)

- De-saturation detection circuit

- Active Miller clamping (AMC) support

- Validated at 225°C for 5000 hours (and still on-going)

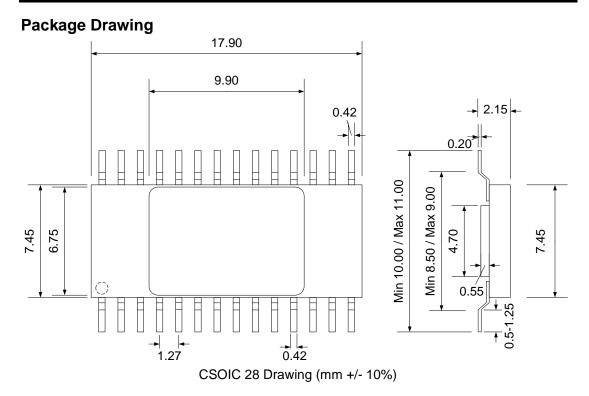

- Package: CSOIC28

### Applications

- Intelligent Power Modules (IPM)

- Power conversion, power generation and actuator controls in aeronautics

- Solar inverters

- Motor drives, battery chargers and DC-DC converters in EV / HEV

- Power conversion and motor drive in railway

- Switched mode power supplies (SMPS)

- Wind turbine power converters

## **Functional Block Diagram**

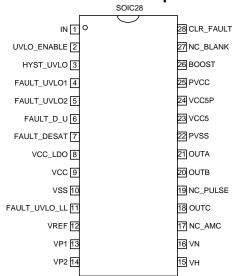

# Package Configurations and Pin Description:

| Pin # | Pin Name          | Pin Description                                                                                                                                                                                                                                                                                                                              |  |  |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | IN                | Schmitt triggered input of the driver. 5V CMOS input with respect to VSS.                                                                                                                                                                                                                                                                    |  |  |

| 2     | UVLO_ENABLE       | Positive input of the under-voltage lockout (UVLO) comparator. The UVLO threshold is set compar-<br>ing the supply voltage multiplied by (RUVLO2/(RUVLO2+RUVLO3)) with the comparator threshold<br>Vth <sub>UVLO</sub> (≅2.5V)                                                                                                               |  |  |

| 3     | HYST_UVLO         | Open-drain output providing a feedback of the UVLO signal in order to set the hysteresis of the UVLO threshold.<br>The drain is open when UVLO=1 (supply voltage above the threshold).                                                                                                                                                       |  |  |

| 4     | FAULT_UVLO1       | Open-drain output for the under-voltage lockout (UVLO) FAULT signal. This output is pulled up<br>when the supply voltage is below UVLO threshold.                                                                                                                                                                                            |  |  |

| 5     | FAULT_UVLO2       | Open-drain output for the under-voltage lockout (UVLO) FAULT signal. This output is pulled up<br>when the supply voltage is below UVLO threshold.                                                                                                                                                                                            |  |  |

| 6     | FAULT_D_U         | Open-drain output combining FAULT_UVLO and FAULT_DESAT signals.<br>This output in pulled down when the supply voltage is below UVLO threshold or when a desatura-<br>tion has been detected.                                                                                                                                                 |  |  |

| 7     | FAULT_DESAT       | Open-drain output for the desaturation FAULT signal.<br>This output is pulled down when a desaturation has been detected.                                                                                                                                                                                                                    |  |  |

| 8     | VCC_LDO           | Positive power supply of the internal voltage regulator. Connect to an external supply voltage from 7V to 30V.                                                                                                                                                                                                                               |  |  |

| 9     | VCC               | Positive power supply. Connect to an external supply voltage from 7V to 30V.                                                                                                                                                                                                                                                                 |  |  |

| 10    | VSS               | Negative power supply. Connect to ground or to a negative supply when a negative drive is neces-<br>sary.                                                                                                                                                                                                                                    |  |  |

| 11    | FAULT_UVLO_LL     | Logic level output for the under-voltage lockout (UVLO) FAULT signal.<br>This output is low when the supply voltage is below UVLO threshold.                                                                                                                                                                                                 |  |  |

| 12    | VREF              | Midpoint of RD22-RD21 resistor divider (available if external tuning is necessary)                                                                                                                                                                                                                                                           |  |  |

| 13    | VP1               | First positive input of the DESAT comparator                                                                                                                                                                                                                                                                                                 |  |  |

| 14    | VP2               | First positive input of the DESAT comparator                                                                                                                                                                                                                                                                                                 |  |  |

| 15    | VH                | Connected to VCC5P through a resistor to set the hysteresis voltage of the DESAT comparator                                                                                                                                                                                                                                                  |  |  |

| 16    | VN                | Negative input of the DESAT comparator                                                                                                                                                                                                                                                                                                       |  |  |

| 17    | NC_AMC            | To be bypassed to VSS by a capacitor in order to set the time constant $t_{\text{amc}}$ (refer to OUTC output pin description)                                                                                                                                                                                                               |  |  |

| 18    | OUTC              | Output of Pre-driver C (5V/250mA output buffer)<br>This output is used to drive an external N-channel MOSFET transistor used for Active Miller<br>Clamping. It inverts OUTA on rising edge of OUTA. It inverts and delays (by $t_{amc}$ ) OUTA on falling<br>edges of OUTA. The duration of $t_{amc}$ is set by the capacitor on node NC_AMC |  |  |

| 19    | NC_PULSE          | To be bypassed to VSS by a capacitor in order to set the pulse width on OUTB output. This pulse<br>is triggered by the rising edge of the input signal on node IN.                                                                                                                                                                           |  |  |

| 20    | OUTB              | Output of Pre-driver B (5V/250mA output buffer)<br>This output is used to drive Normally-Off SiC JFET. It generates a short pulse triggered by rising<br>edge on IN input. The duration is set by the capacitor on node NC_PULSE                                                                                                             |  |  |

| 21    | OUTA              | Output of Pre-driver A (5V/250mA output buffer)                                                                                                                                                                                                                                                                                              |  |  |

| 22    | PVSS              | Negative power supply of driver output stage. To be connected to VSS                                                                                                                                                                                                                                                                         |  |  |

| 23    | VCC5<br>(input)   | 5V positive power supply of the control logic. To be connected VCC5P                                                                                                                                                                                                                                                                         |  |  |

| 24    | VCC5P<br>(output) | 5V positive output with respect to VSS. To be bypassed to VSS by a decoupling capacitor (of appropriate value for the application).                                                                                                                                                                                                          |  |  |

| 25    | PVCC              | Positive power supply of the boost diode. Connect to an external supply voltage from 7V to 30V.                                                                                                                                                                                                                                              |  |  |

| 26    | BOOST             | Cathode of the on-chip boost diode                                                                                                                                                                                                                                                                                                           |  |  |

| 27    | NC_BLANK          | To be bypassed to VSS by a capacitor in order to set the blanking time of the desaturation com-<br>parator. After the blanking time, the result of the FAULT comparator is read.                                                                                                                                                             |  |  |

| 28    | CLR_FAULT         | Schmitt triggered input of the FAULT state clearing signal. 5V CMOS input with respect to VSS.                                                                                                                                                                                                                                               |  |  |

# **Absolute Maximum Ratings**

| Parameter                     | Min.         | Max.      | Units |

|-------------------------------|--------------|-----------|-------|

| (VCC-VSS)                     | -0.5         | 35        | V     |

| (VCC5P-VSS)                   | -0.5         | 6         | V     |

| (BOOST-VCC)                   | -0.5         | 35        | V     |

| OUTA, OUTB, OUTC              | PVSS-0.5     | VCC5P+0.5 | V     |

| IN, CLR_FAULT                 | VSS-0.5      | VCC5P+0.5 | V     |

| VP1, VP2                      | VSS-0.5      | VCC+0.5   | V     |

| VN                            | VSS-0.5      | VCC+0.5   | V     |

| UVLO_ENABLE                   | VSS-0.5      | VCC+0.5   | V     |

| NC_BLANK, NC_PULSE, NC_AMC    | VSS-0.5      | VCC5P+0.5 | V     |

| (VSS-PVSS)                    | -0.5         | 0.5       | V     |

| (PVCC-PVSS)                   | -0.5         | 35        | V     |

| Junction Temperature          |              | 250       | °C    |

| ESD Rating (Human Body Model) | 2 (expected) |           | kV    |

| Max power dissipation         |              | 1         | W     |

# **Operating conditions**

| Parameter                  | Min. | Max.  | Units |

|----------------------------|------|-------|-------|

| (VCC-VSS)                  | 0    | 30    | V     |

| (VCC5P-VSS)                | 0    | 5.5   | V     |

| (BOOST-VCC)                | 0    | 35    | V     |

| IN, CLR_FAULT              | VSS  | VCC5P | V     |

| VP1, VP2                   | VSS  | VCC   | V     |

| VN                         | VSS  | VCC   | V     |

| UVLO_ENABLE                | VSS  | VCC   | V     |

| NC_BLANK, NC_PULSE, NC_AMC | VSS  | VCC5P | V     |

| (VSS-PVSS)                 | -0.1 | 0.1   | V     |

| (PVCC-PVSS)                | 0    | 30    | V     |

| Junction Temperature       |      | 225   | °C    |

| Max power dissipation      |      | 0.5   | W     |

Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Frequent or extended exposure to absolute maximum rating conditions or above may affect device reliability.

## **Electrical Characteristics**

Unless otherwise stated: (VCC-VSS)=15V,  $\underline{T}_{j}=25^{\circ}C$ . Bold underlined values indicate values over the whole operational temperature range (-55°C < T j < +225°C).

| Parameter                                                                           | Condition                                             | Min          | Тур    | Max          | Units |

|-------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|--------|--------------|-------|

| External Power Supply                                                               | Condition                                             |              | 196    | max          | onno  |

| External Power Supplies <sup>1</sup>                                                | If internal linear voltage regulator<br>is bypassed   | 4.75         |        | 5.25         | V     |

| (PVCC & VCC) versus VSS                                                             | If internal linear voltage regula-<br>tor is used     | 7            |        | 30           | V     |

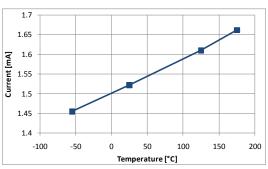

| VCC quiescent current                                                               | Ta = 25°C                                             |              | 1.53   | <u>2.5</u>   | mA    |

| VCC_LDO quiescent<br>current                                                        |                                                       |              |        | <u>0.5</u>   | mA    |

| PVCC quiescent current                                                              |                                                       |              |        | 0.1          | mA    |

| VCC average current                                                                 | IN signal = 20kHz, 50% duty<br>cycle, Ta = 25°C       |              | 1.73   |              | mA    |

| 5V Internal Power Supply                                                            |                                                       |              |        |              |       |

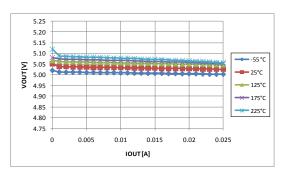

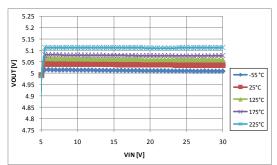

| Internal 5V Power Supply <sup>2</sup><br>(VCC5P) versus VSS                         | (VCC-VSS) from 7V to 30V,<br>lout from 0.25mA to 25mA | <u>4.75</u>  | 5      | <u>5.25</u>  | V     |

| Output Capacitor C5P                                                                | Capacitor value at Tamb=25°C                          |              | 1      |              | μF    |

| Output Current                                                                      |                                                       | 0.25         | 1      | 25           | mA    |

| Initial Accuracy                                                                    | (VCC-VSS)= 15V; lout=2.5mA                            | 0.25         | +/-1.2 | 23           | %     |

| Drift with temperature                                                              | (VCC-VSS)= 15V; lout=2.5mA                            |              | 0.5    | -            | mV/°C |

| Line Regulation                                                                     | (VCC-VSS) from 7V to 30V;                             |              | +/-0.1 |              | %     |

| Load Regulation                                                                     | lout=2.5mA<br>(VCC-VSS)= 15V; lout from               |              | 1.25   |              | %     |

|                                                                                     | 2.5mA to 25mA                                         |              | 0      |              | 70    |

| Under-voltage Lockout (UV                                                           | LO)                                                   |              |        | -            | 1     |

| Internal UVLO comparator threshold voltage                                          |                                                       | <u>2.375</u> | 2.5    | <u>2.625</u> | V     |

| Internal UVLO comparator<br>threshold voltage:<br>absolute accuracy                 | (PVCC-PVSS) from 7V to 30V                            | <u>-5</u>    |        | <u>5</u>     | %     |

| Open-drain transistor ON-<br>Resistance                                             | Note: transistor drain is<br>HYST_UVLO pin_           |              | 1K     |              | Ω     |

| Delay from UVLO_ENABLE to FAULT_UVLO                                                | 500mV overdrive <sup>3</sup>                          |              | 100    |              | ns    |

| Delay from UVLO_ENABLE<br>to driver outputs (OUTA and<br>OUTB) when VCC goes<br>low | CLoad=0.5nF                                           |              | 100    |              | ns    |

| UVLO_ENABLE Max forced<br>input current <sup>4</sup>                                |                                                       |              |        | <u>3</u>     | mA    |

| UVLO_ENABLE Max input<br>leakage current                                            |                                                       | <u>-3</u>    |        | <u>+3</u>    | μA    |

| Input signal (IN, CLR_FAULT)                                                        |                                                       |              |        |              |       |

| Input start threshold                                                               |                                                       | <u>3.03</u>  | 3.43   | 3.83         | V     |

| Input stop threshold                                                                |                                                       | <u>1.1</u>   | 1.39   | 1.68         | V     |

| Hysteresis                                                                          |                                                       | 1.68         | 2.04   | 2.39         | V     |

| Pre-Drivers                                                                         |                                                       |              |        |              |       |

| Output sink current<br>(OUTA/B)                                                     |                                                       |              | 0.25   |              | А     |

| Output source current<br>(OUTA/B)                                                   |                                                       |              | 0.25   |              | А     |

| Propagation delay when<br>output rising (IN→OUTA/B)                                 | CLoad=0.5nF<br>(50%→ 50%)                             |              | 30     |              | ns    |

| Propagation delay when                                                              | (50%→ 50%)<br>CLoad=0.5nF                             |              |        |              |       |

| output falling (IN→OUTA/B)                                                          | (50%→ 50%)                                            |              | 30     |              | ns    |

| Rise Time (10%-90%)                                                                 | CLoad=0.5nF                                           |              | 10     |              | ns    |

| Fall Time (10%-90%)                                                                 | CLoad=0.5nF                                           |              | 10     | <u> </u>     | ns    |

| Pulse time t <sub>pulse</sub> for a given                                           | $C_{PULSE}=30 pF^5$                                   | <u>75</u>    | 100    | <u>125</u>   | ns    |

$^1$  Voltage externally supplied to the chip  $^2_{\rm 2}$  5V supply generated on-chip

<sup>3</sup> This delay is obtained for a step from 2V to 3V with a rise time of 10ns at node UVLO\_ENABLE <sup>4</sup> Comparator differential voltage (V+-V-) is clamped to about 5V by current limiting diodes able to absorb 3mA

<sup>5</sup> This supposes an external Ceramic COG capacitor with a 50ppm/°C temperature coefficient

#### **CHT-THEMIS-Power Transistor Driver Controller -**DATASHEET

#### (Last Modification Date)

| Parameter                                                                                    | Condition                                                                                                                 | Min         | Тур | Max         | Units |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------|-----|-------------|-------|

| external capacitor                                                                           |                                                                                                                           |             |     |             |       |

| Pulse time t <sub>pulse</sub> range                                                          | C <sub>PULSE</sub> from 15pF to 150pF                                                                                     | 50          |     | 500         | ns    |

| Active Miller Clamping (AMC                                                                  | C) Pre-driver                                                                                                             |             |     |             |       |

| AMC delay t <sub>AMC</sub> for a given external capacitor                                    | C <sub>AMC</sub> =30pF <sup>6</sup>                                                                                       | <u>150</u>  | 200 | <u>250</u>  | ns    |

| AMC delay range t <sub>AMC</sub> range                                                       | C <sub>AMC</sub> from 15pF to 220pF                                                                                       | 100         |     | 1500        | ns    |

| FAULT/DESAT comparator                                                                       |                                                                                                                           |             |     |             | -     |

| Iref*RD22                                                                                    |                                                                                                                           | <u>2.25</u> | 2.5 | <u>2.75</u> | V     |

| Effective threshold range w/<br>respect to ND node for<br>Normally On SiC JFET               | Vp1 to NS, Vp2 to VSS;<br>Programmable with external<br>resistors RD11, RD12 with the<br>equation of note <sup>7</sup>    | 2.5         |     | 7.5         | v     |

| Effective threshold range w/<br>respect to ND node for<br>Normally Off SiC JFET              | Vp1 to VSS, Vp2 floating;<br>Programmable with external<br>resistors RD11, RD12 with the<br>equation of note <sup>8</sup> | <u>2.5</u>  |     | <u>7.5</u>  | v     |

| VN max forced input cur-<br>rent <sup>9</sup>                                                |                                                                                                                           |             |     | <u>10</u>   | mA    |

| VN max input leakage cur-<br>rent                                                            |                                                                                                                           | <u>-1</u>   |     | <u>+1</u>   | μA    |

| Delay from VN to<br>FAULT_DESAT output                                                       | IN=1 for t> t <sub>BLANK</sub> , 500mV over-<br>drive <sup>10</sup>                                                       |             | 100 |             | ns    |

| Blanking time t <sub>BLANK</sub> accura-<br>cy for fixed external capaci-<br>tor             | C <sub>BLANK</sub> =300pF <sup>11</sup>                                                                                   | <u>3</u>    | 4   | <u>5</u>    | μs    |

| Blanking time range                                                                          | C <sub>BLANK</sub> from 15pF to 600pF                                                                                     | 0.2         |     | 8           | μs    |

| Delay t <sub>AL_DESAT</sub> between<br>FAULT_DESAT pulled<br>down and OUTA forced to<br>ZERO | In case of DESAT Fault event                                                                                              | 100         | 200 | 300         | ns    |

| Hysteresis open-drain tran-<br>sistor (Vh input) ON-<br>Resistance                           |                                                                                                                           |             | 1K  |             | Ω     |

|                                                                                              | FAULT Outputs (FAULT_UVLO1, FAULT_UVLO2, FAULT_DESAT & FAULT_D_U)                                                         |             |     |             |       |

| Open-drain transistor ON-<br>Resistance                                                      |                                                                                                                           | <u>40</u>   | 60  | <u>120</u>  | Ω     |

<sup>&</sup>lt;sup>6</sup>This assumes an external Ceramic COG capacitor with a 50ppm/°C temperature coefficient

<sup>&</sup>lt;sup>7</sup>Case Normally-On JFET: Vth<sub>ND</sub>=(RDD11+RDD12)\*(Iref\*RD22)/RDD12 with the constraint of RDD11//RDD12=R' <sup>8</sup>Case Normally-Off JFET: Vth<sub>ND</sub>=(RDD11+RDD12)\*(Iref\*RD22)/RDD12  $\frac{9}{2}$ (Vref-Vn) is clamped to about 5V by current limiting diodes able to absorb 10mA

<sup>&</sup>lt;sup>10</sup> This delay is obtained for a step from 2V to 3V with a rise time of 10ns at node VN, the effective threshold being set to 2.5V <sup>11</sup>This assumes an external Ceramic COG capacitor with a 50ppm/°C temperature coefficient

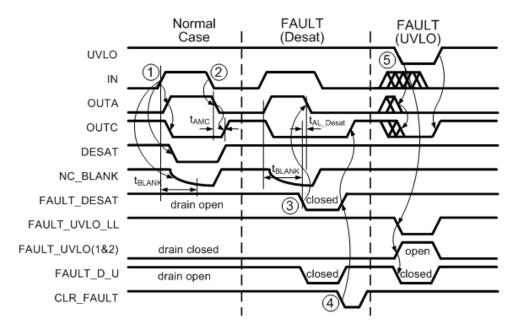

## **Control Logic Timing Diagram**

#### Main Events:

#### ① Rising input 'IN' signal:

- $\rightarrow$  The output 'OUTA' rises up after a propagation delay

- $\rightarrow$  The output 'OUTC' falls down after a propagation delay

$\rightarrow$  The output of the DESAT comparator falls down, as a consequence of the turn ON of the external power transistor

→ The node NC\_BLANK discharges with a time constant  $t_{BLANK}=R_{BLANK}*C_{BLANK}$ . As the output of the DESAT comparator falls down before the end of the blanking time  $t_{BLANK}$ , no DESAT fault occurs and node FAULT\_DESAT remains high (FAULT\_DESAT is active LOW).

#### ② Falling input 'IN' signal:

- $\rightarrow$  The output 'OUTA' fall down after a propagation delay

- $\rightarrow$  The output 'OUTC' rise up after a time constant t\_{AMC}=R\_{AMC}\*C\_{AMC}

$\rightarrow$  The output of the DESAT comparator rises up, as a consequence of the turn OFF of the external power transistor

# ③ DESAT Fault Event: The output of the DESAT comparator doesn't fall down after a rising input 'IN' signal

- $\rightarrow$  After time constant t<sub>BLANK</sub>, the output 'FAULT\_DESAT' is forced to return to 0

- $\rightarrow$  After time constant (t<sub>BLANK</sub>+t<sub>AL\_DESAT</sub>), the output 'OUTA' is forced to return to 0

- $\rightarrow$  The output 'OUTC' is hold to 0 until the DESAT Fault clear (see 4)

#### ④ CLEAR\_FAULT signal is sent by the controller (negative pulse)

- $\rightarrow$  The internal DESAT fault state is cleared and FAULT\_DESAT output rises up

- $\rightarrow$  The output 'OUTC' is released and goes to not(OUTA)

#### **(5)** UVLO Fault Event: The output of the UVLO comparator falls down

$\rightarrow$  The output 'OUTA' is forced to zero

$\rightarrow$  The output 'OUTC' is also forced to zero, aiming to put the external AMC transistor in high impedance (drain open)

$\rightarrow$ The output 'FAULT\_UVLO\_LL' fall down (FAULT\_UVLO\_LL is active LOW)

$\rightarrow$ Outputs 'FAULT\_UVLO(1&2)' rise up (FAULT\_UVLO(1&2) are active HIGH)

# Typical Performance Characteristics (VCC-VSS = 15V)

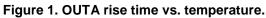

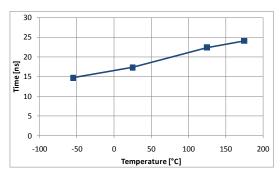

Figure 3. OUTA rising propagation delay vs. temperature.

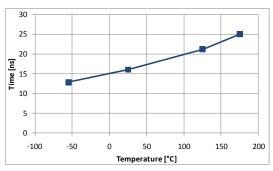

Figure 5.  $t_{PULSE}$  versus temperature (C<sub>PULSE</sub>=100pF).

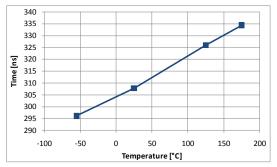

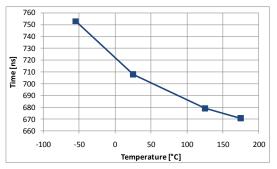

Figure 7. UVLO threshold versus temperature.

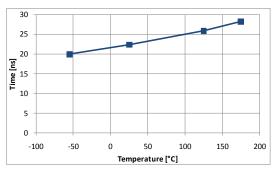

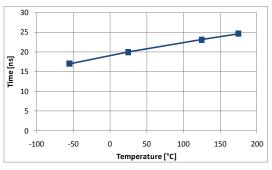

Figure 2. OUTA fall time vs. temperature.

Figure 4 OUTA falling propagation delay vs. temperature.

Figure 6.  $t_{AMC}$  versus temperature (C<sub>AMC</sub>=100pF).

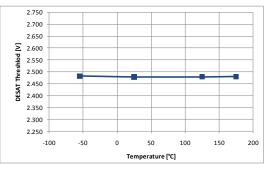

Figure 8. DESAT threshold versus temperature.

## CHT-THEMIS-Power Transistor Driver Controller -DATASHEET

(Last Modification Date)

# Application diagrams

## **General Description**

CHT-THEMIS is the controller of the CHT-THEMIS / CHT-ATLAS chipset. The chipset is a high-temperature power switch driver specifically designed to drive Silicon Carbide (SiC) power transistors including normally-On and normally-Off JFETs, MOSFETs and BJTs. In this section, some of the different blocks shown in the Block Diagram section (page 2) are described and formulas are given for the selection of the external components for the typical applications presented in the last section.

#### **Under Voltage Detection**

The aim of this function is to allow the user to specify a threshold voltage for the power supply (VCC-VSS) under which the driver outputs (OUTA, OUTB, and OUTC) are pulled down to VSS and a fault is reported to the logic part of the system through the FAULT\_UVLO\_LL/FAULT\_UVLO1/FAULT\_UVLO2 outputs. For a given threshold voltage, noted  $V_{UVLO}$ , the  $R_{UVLO1}$  and  $R_{UVLO2}$  are obtained as follows:

- Choose  $R_{UVLO2}$  to satisfy (V\_UVLO-VSS)/  $R_{UVLO2}$  >> 3µA (leakage current on UVLO\_ENABLE pin)

- Then, compute  $R_{UVLO1}$  with the desired  $V_{UVLO}$  using the following equation:

$$\mathsf{R}_{\mathsf{UVLO1}} = \mathsf{R}_{\mathsf{UVLO2}} \left( \frac{\mathsf{V}_{\mathsf{UVLO}} - \mathsf{VSS}}{2.5} - 1 \right)$$

To avoid oscillation when (VCC-VSS) are close to the UVLO threshold, an adjustable hysteresis can be configured through the resistor  $R_{HYST}$  which value can be obtained as follows:

- The R<sub>HYST</sub> must satisfy the condition R<sub>HYST</sub> >> 1kΩ (R<sub>ON</sub> of the hysteresis pool-down transistor)

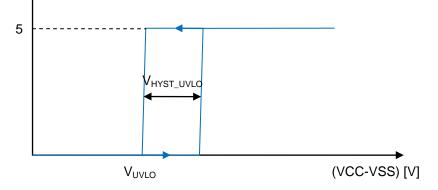

- Then, compute  $R_{HYST}$  with the desired  $V_{HYST_UVLO}$  (see Figure 12 for the definition of  $V_{HYST_UVLO}$ ):

$$R_{HYST} = \frac{2.5 \text{-VSS}}{\frac{V_{HYST\_UVLO}}{R_{UVLO1}} - \left(\frac{1}{R_{UVLO1}} + \frac{1}{R_{UVLO2}}\right) * \text{VSS}}$$

Example: for VSS=0; V<sub>UVLO</sub>=7.5V; V<sub>HYST\_UVLO</sub>=0.5V, and by choosing R<sub>UVLO2</sub>=100k $\Omega$  we obtain: R<sub>UVLO1</sub>=200k $\Omega$  and R<sub>HYST</sub>=1M $\Omega$

V<sub>FAULT\_UVLO\_LL</sub> [V]

#### **De-saturation detection**

The purpose of the DESAT function is to detect that the voltage at the drain of the power switch, in "ON" state, is lower than a given threshold (defined by external resistors  $R_{D11}$ ,  $R_{D12}$ , and R'). This informs the logic part of the system about possible damage of the power switch through FAULT\_DESAT output. The values of the external resistors  $R_{D11}$ ,  $R_{D12}$  and R' can be obtained as follows:

- The value of R' must satisfy the following condition R'=RD11//RD12 to remove the VSS contribution from the de-saturation voltage sensing

- Then, compute R<sub>D11</sub> and R<sub>D12</sub> with the desired de-saturation threshold V<sub>DESAT</sub> and a given value of R' (small enough to avoid VN leakage current < 10nA):</li>

$$R_{D11} = \frac{R'^{*} (V_{DESAT} + V_{SENSE\_DIODE} + V_{NS})}{2.5 + V_{NS}}$$

$$R_{D12} = \frac{R_{D11}^{*} R'}{R_{D11} - R'}$$

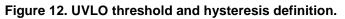

To avoid oscillation when  $V_{DEASAT}$  is close to the de-saturation threshold, an adjustable hysteresis can be configured through the resistor  $R_H$  which value can be obtained as follows for a given de-saturation hysteresis  $V_{HYST\_DESAT}$ :

$$R_{H}=R_{D11}*\frac{3.3}{V_{HYST_{DESAT}}}$$

Figure 13. DESAT threshold and hysteresis definition.

At system level, the de-saturation detection should only be taken into account after a defined time following the low-to-high transition on "IN" input. This "blanking" time  $t_{BLANK}$  is adjusted by an external capacitor  $C_{BLANK}$  on the NC\_BLANK pin and is used inside the Control Logic block to determine if a de-saturation took place or not. The  $t_{BLANK}$  delay must be higher than the de-saturation comparator delay and can be calculated using the following equation:

Example: for R'=100k $\Omega$ , V<sub>DESAT</sub>=2V, V<sub>SENSE\_DIODE</sub>=1V, and V<sub>HYST\_DESAT</sub>=0.5V we obtain: R<sub>D11</sub>=120k $\Omega$ , R<sub>D12</sub>=600k $\Omega$ , and R<sub>H</sub>=792k $\Omega$ .

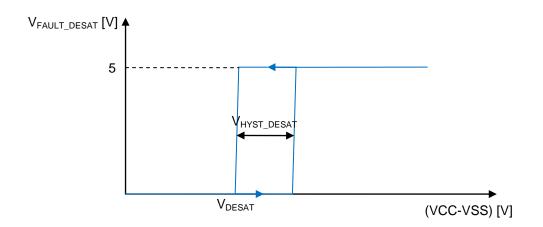

#### Active Miller Clamping

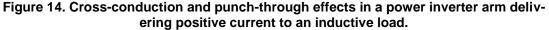

The purpose of the Active Miller Clamping (AMC) feature is to avoid parasitic crossconduction (positive kick on VGS) or punch-through (negative kick on VGS) during different switching phases in FET bridge arms (high/low side switches) in the context of power inverter application (see Figure 14).

Cross-conduction effect can happen with all types of FET devices while punch-through effect is more related to JFET devices.

These 2 effects are due to drain-to-gate coupling through the Miller capacitance of the FETs. They are further enhanced with the gate resistance which is necessary to kill the ringing effect due to parasitic inductances. The AMC provides a low impedance path, without series resistance, to maintain the gate voltage at its desired value to turn OFF the JFET properly with reduced risk of cross-conduction/punch-through. Figure 14 shows the cross-conduction and punch-through effects in a power inverter arm delivering positive current to an inductive load. In this case, the AMC feature in the low side driver provides a solution to significantly reduce the risk of cross-conduction/punch-through effects. Similarly, the same effects can be observed at the high side in the case of a power inverter arm delivering negative current.

For proper operation, the AMC delay ( $t_{AMC}$ ) must be carefully adjusted and smaller than the non-overlapping delay between low and high side PWM inputs. This is made possible thanks to the external capacitor  $C_{AMC}$  which is related to  $t_{AMC}$  as:

## Support of Normally-Off devices

Unlike the normally-on JFET, the gate-source junction of the normally-off SiC JFET is forward biased in the device conduction state. In addition to the dynamic current for charg-ing/discharging the total gate capacitance, some steady-state current has to be provided to maintain conduction after the device has been switched on.

The two channels of CHT-ATLAS can be combined to deliver both dynamic and steady-state currents (please refer to application diagrams).

Channel A must be driven with the regular PWM control signal (OUTA) while channel B must be driven by the second control signal (OUTB) giving a shorter impulse at the turn-on. The pulse width  $t_{\text{PULSE}}$  of this second control signal can be adjusted thanks to the external capacitor  $C_{\text{PULSE}}$  as:

t<sub>PULSE</sub>=3333 \* C<sub>PULSE</sub>

# **Ordering Information**

| Ordering Reference     | Package | Temperature Range | Marking      |

|------------------------|---------|-------------------|--------------|

| CHT-TIT9570C-CSOIC28-T | CSOIC28 | -55°C to +225°C   | CHT-TIT9570C |

# Contact & Ordering

## CISSOID S.A.

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium<br>T : +32 10 48 92 10 - F: +32 10 88 98 75<br>Email: <u>sales@cissoid.com</u> |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: http://www.cissoid.com                                                                                                         |

## Disclaimer

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.