### Twenty-Five Years Of Quality Through Innovation

| FEATURES                                      |                 |  |  |  |  |

|-----------------------------------------------|-----------------|--|--|--|--|

| VERY HIGH INPUT IMPEDANCE                     |                 |  |  |  |  |

| HIGH GATE BREAKDOWN                           |                 |  |  |  |  |

| ULTRA LOW LEAKAGE                             |                 |  |  |  |  |

| LOW CAPACITANCE                               |                 |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS (NOTE 1)             |                 |  |  |  |  |

| (T <sub>A</sub> =25°C unless otherwise noted) |                 |  |  |  |  |

| Drain-Source or Drain-Gate Voltage (NOTE 2)   |                 |  |  |  |  |

| 3N165                                         | 40 V            |  |  |  |  |

| 3N166                                         | 30 V            |  |  |  |  |

| Gate-Gate Voltage                             | ±80 V           |  |  |  |  |

| Drain Current (NOTE 2)                        | 50 mA           |  |  |  |  |

| Storage Temperature                           | -55°C to +150°C |  |  |  |  |

| Operating Temperature                         | -55°C to +150°C |  |  |  |  |

| Lead Temperature (Soldering, 10 sec.)         | +300°C          |  |  |  |  |

| Power Dissipation (One Side)                  | 300 mW          |  |  |  |  |

| Total Derating above 25°C                     | 4.2 mW/°C       |  |  |  |  |

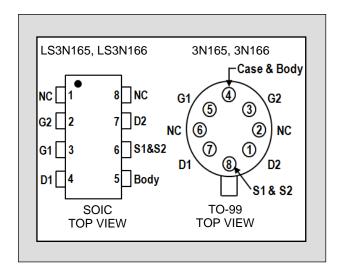

## LS/3N165, LS/3N166

# MONOLITHIC DUAL P-CHANNEL ENHANCEMENT MODE **MOSFET**

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub>=25°C and V<sub>BS</sub>=0 unless otherwise noted)

|                                   |                                 | 3N165 & LS3N165 & LS3N166 |      |      |      |       |                                                              |                        |                     |  |

|-----------------------------------|---------------------------------|---------------------------|------|------|------|-------|--------------------------------------------------------------|------------------------|---------------------|--|

| SYMBOL                            | CHARACTERISTIC                  | MIN                       | MAX  | MIN  | MAX  | UNITS | CONDITIONS                                                   |                        |                     |  |

| I <sub>GSSR</sub>                 | Gate Reverse Leakage Current    |                           | 10   |      | 100  |       | V <sub>GS</sub> =40V                                         |                        |                     |  |

| I <sub>GSSF</sub>                 | Gate Forward Leakage Current    |                           | -10  |      | -100 |       | V <sub>GS</sub> =-40V                                        |                        |                     |  |

|                                   |                                 |                           | -25  |      |      | pА    | T <sub>A</sub> =+125°C                                       |                        |                     |  |

| I <sub>DSS</sub>                  | Drain to Source Leakage Current |                           | -200 |      | -200 |       | V <sub>DS</sub> =-20 V, V <sub>GS</sub> =V <sub>BS</sub> =0V |                        |                     |  |

| I <sub>SDS</sub>                  | Source to Drain Leakage Current |                           | -400 |      | -400 |       | V <sub>SD</sub> =-20 V, V <sub>GD</sub> =V <sub>DB</sub> =0V |                        |                     |  |

| I <sub>D(on)</sub>                | On Drain Current                | -5                        | -30  | -5   | -30  | mA    | V <sub>DS</sub> =-15V                                        | V <sub>GS</sub> =-10 V | V <sub>SB</sub> =0V |  |

| $V_{GS(th)}$                      | Gate Source Threshold Voltage   | -2                        | -5   | -2   | -5   | V     | V <sub>DS</sub> =-15V                                        | I <sub>D</sub> =-10μA  | V <sub>SB</sub> =0V |  |

| $V_{GS(th)}$                      | Gate Source Threshold Voltage   | -2                        | -5   | -2   | -5   | V     | $V_{DS}=V_{GS}$                                              | I <sub>D</sub> =-10μA  | V <sub>SB</sub> =0V |  |

| r <sub>DS(on)</sub>               | Drain Source ON Resistance      |                           | 300  |      | 300  | ohms  | V <sub>GS</sub> =-20V                                        | I <sub>D</sub> =-100μA | V <sub>SB</sub> =0V |  |

| <b>g</b> fs                       | Forward Transconductance        | 1500                      | 3000 | 1500 | 3000 | μS    | V <sub>DS</sub> =-15V                                        | I <sub>D</sub> =-10mA  | f=1kHz              |  |

| gos                               | Output Admittance               |                           | 300  |      | 300  | μS    |                                                              | $V_{SB}$ =0 $V$        |                     |  |

| C <sub>lss</sub>                  | Input Capacitance               |                           | 3.0  |      | 3.0  |       |                                                              |                        |                     |  |

| C <sub>rss</sub>                  | Reverse Transfer Capacitance    |                           | 0.7  |      | 1.0  | pF    | $V_{DS}$ =-15 $V$                                            | $I_D=-10mA$            | f=1MHz              |  |

| Coss                              | Output Capacitance              |                           | 3.0  |      | 3.0  |       | ( <u>NOTE 3</u> )                                            | V <sub>SB</sub> =0V    |                     |  |

| R <sub>E</sub> (Y <sub>Is</sub> ) | Common Source Forward           | 1200                      |      |      |      | μS    | V <sub>DS</sub> =-15V                                        | I <sub>D</sub> =-10mA  | f=100MHz            |  |

|                                   | Transconductance                |                           |      |      |      |       | ( <u>NOTE 3</u> )                                            | V <sub>SB</sub> =0V    |                     |  |

#### **MATCHING CHARACTERISTICS 3N165**

|                                    |                                            | LIMITS |      |       |                          |                         |                     |                     |  |

|------------------------------------|--------------------------------------------|--------|------|-------|--------------------------|-------------------------|---------------------|---------------------|--|

| SYMBOL                             | CHARACTERISTIC                             | MIN.   | MAX. | UNITS | CONDITIONS               |                         |                     |                     |  |

| G <sub>fs1</sub> /G <sub>fs2</sub> | Forward Transconductance Ratio             | 0.90   | 1.0  |       | V <sub>DS</sub> =-15V    | I <sub>D</sub> =-500 μA | f=1kHz              | V <sub>SB</sub> =0V |  |

| V <sub>GS1-2</sub>                 | Gate Source Threshold Voltage Differential |        | 100  | mV    | V <sub>DS</sub> =-15V    | I <sub>D</sub> =-500 μA | V <sub>SB</sub> =0V |                     |  |

| $\Delta V_{GS1-2}/\Delta T$        | Gate Source Threshold Voltage Differential |        | 100  | μV/ºC | V <sub>DS</sub> =-15V    | I <sub>D</sub> =-500 μA | V <sub>SB</sub> =0V |                     |  |

|                                    | Change with Temperature                    |        |      |       | T <sub>A</sub> =-55°C to | o = +125°C              |                     |                     |  |

#### **NOTES:**

- 1. MOS field effect transistors have extremely high input resistance and can be damaged by the accumulation of excess static charge. To avoid possible damage to the device while wiring, testing, or in actual operation, follow these procedures:

To avoid the build-up of static charge, the leads of the devices should remain shorted together with a metal ring except when being tested or used. Avoid unnecessary handling. Pick up devices by the case instead of the leads. Do not insert or remove devices from circuits with the power on, as transient voltages may cause permanent damage to the devices.

- 2. Per transistor.

- 3. For design reference only, not 100% tested.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Linear Integrated Systems (LIS) is a 25-year-old, third-generation precision semiconductor company providing high-quality discrete components. Expertise brought to LIS is based on processes and products developed at Amelco, Union Carbide, Intersil and Micro Power Systems by company President John H. Hall. Hall, a protégé of Silicon Valley legend Dr. Jean Hoerni, was the director of IC Development at Union Carbide, co-founder and vice president of R&D at Intersil, and founder/president of Micro Power Systems.