# Comlinear CLC436 200MHz, ±15V, Low-Power Voltage Feedback Op Amp

### General Description

range and signal-to-noise ratio.

reconstruction DACs.

The Comlinear CLC436 is a high-performance, low power, voltage-feedback operational amplifier that has been designed for a wide range of low-cost applications. The CLC436 is specified to operate from dual ±5V to dual ±15V power supplies. Operating from ±5V supplies, the unity gain stable CLC436 consumes a mere 23mW of power and features a 150MHz bandwidth and 850V/µs slew rate. Operating from ±15V power supplies, the CLC436 consumes only 69mW (I<sub>cc</sub> = 2.3mA) to provide a 200MHz unity-gain bandwidth, a very fast 2400V/μs slew rate and 13ns rise/fall times (5V step). At ±15V, the device also provides large signal swings (>20Vpp) to give high dynamic

As a low-power NTSC or PAL video line-driver, the CLC436 delivers low differential gain and phase errors (0.2%, 1.2°) and very high output drive current of 80mA. When used as a video ADC driver, the CLC436 offers low Total Harmonic Distortion (THD) and high Spurious Free Dynamic Range (SFDR). Because of it's voltage feedback topology, the CLC436 allows use of reactive elements in the feedback path and can be configured as an excellent active filter for video-

The CLC436's combination of low cost and high performance in addition to its low-power voltage-feedback topology make it a versatile signal conditioning building block for a wide range of price-sensitive applications.

#### **Features**

- 2.3mA supply current

- 200MHz unity-gain bandwidth

- 2400V/µs slew rate

- Unity gain stable

- 110dB common-mode rejection ratio

- 80mA drive current

- >20V<sub>pp</sub> output swing

- ±5V to ±15V supplies

### Applications

- Video line driver

- Video ADC driver

- Desktop Multimedia

- Low powered cable driver

- Video DAC buffer

- Active filters/integrators

- NTSC & PAL video systems

Bandpass Output 9 Magnitude -5 0.1 Frequency (MHz) NC 8 NC Pinout 7 +Vcc 2 DIP & SOIC  $V_{non-inv}$ 6 Vout -V<sub>cc</sub> 5 NC

1996 National Semiconductor Corporation rinted in the U.S.A.

http://www.national.com

| CLC436 Electrical Characteristics ( $V_{cc} = \pm 15V$ , $A_v = +2$ , $R_f = 499\Omega$ , $R_L = 1k\Omega$ ; unless specified)                                                                                             |                                                                                                                                                                                                                                                                                                                             |                                                         |                                                                                                    |                                                                    |                                                                     |                                                                  |                                                    |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------|------------------|

| PARAMETERS                                                                                                                                                                                                                 | CONDITIONS                                                                                                                                                                                                                                                                                                                  | V <sub>cc</sub>                                         | TYP                                                                                                | MiM                                                                | VMAX RATIN                                                          |                                                                  | UNITS                                              | NOTES            |

|                                                                                                                                                                                                                            | CLC436AJ                                                                                                                                                                                                                                                                                                                    |                                                         | 25°                                                                                                | 25°                                                                | 0° to +70°                                                          | -40° to +85°                                                     |                                                    |                  |

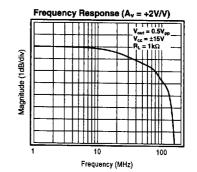

| FREQUENCY DOMAIN RESP<br>-3dB bandwidth                                                                                                                                                                                    | V <sub>out</sub> < 0.5V <sub>pp</sub> (AJP)<br>V <sub>out</sub> < 0.5V <sub>pp</sub> (AJE)<br>V <sub>out</sub> < 10V <sub>pp</sub>                                                                                                                                                                                          | ±15, ±5<br>±15, ±5                                      | 96,55<br>96,55<br>25                                                                               | 50<br>50<br>21                                                     | 50<br>60<br>20                                                      | 50<br>40<br>16                                                   | MHz<br>MHz<br>MHz                                  | B<br>B           |

| -3dB bandwidth A <sub>V</sub> = +1 gain flatness rolloff peaking linear phase deviation differential gain differential phase gain bandwidth product                                                                        | $\begin{array}{l} V_{out}^{\text{V}} < 0.5V_{pp}^{\text{P}},  R_f = 0 \\ V_{out}^{\text{V}} < 0.5V_{pp}^{\text{P}},  R_f = 0 \\ DC \text{ to 20MHz} \\ DC \text{ to 10MHz} \\ DC \text{ to 10MHz} \\ 4.43\text{MHz},  R_L = 150\Omega \\ 4.43\text{MHz},  R_L = 150\Omega \\ V_{out}^{\text{V}} < 2.0V_{pp} \\ \end{array}$ | ±15, ±5<br>±15, ±5                                      | 200,150<br>0.6<br>0<br>0.5<br>0.2<br>1.2<br>200,100                                                | 1.2<br>0.03                                                        | 1.2<br>0.03                                                         | 1.2<br>0.03                                                      | MHz  dB  dB  deg  w  deg  MHz                      | B<br>B           |

| TIME DOMAIN RESPONSE rise and fall time settling time to 0.05% overshoot slew rate                                                                                                                                         | 2V step, $t_r(in) = 5ns$<br>5V step, $t_r(in) = 5ns$<br>2V step, $t_r(in) = 5ns$<br>2V step, $t_r(in) = 5ns$<br>5V step, $t_r(in) = 5ns$                                                                                                                                                                                    | ±15, ±5<br>±15, ±5                                      | 11<br>13<br>36,48<br>0.5<br>2400,850                                                               | 13<br>16<br>42<br>1<br>2000                                        | 14<br>18<br>65<br>2<br>1900                                         | 18<br>20<br>85<br>2<br>1600                                      | ns<br>ns<br>ns<br>%<br>V/µs                        |                  |

| DISTORTION AND NOISE RE 2nd harmonic distortion 3rd harmonic distortion 2nd harmonic distortion 3rd harmonic distortion input voltage noise current noise                                                                  | SPONSE<br>1V <sub>pp</sub> , 1MHz<br>1V <sub>pp</sub> , 1MHz<br>1V <sub>pp</sub> , 5MHz<br>1V <sub>pp</sub> , 5MHz<br>0 1kHz<br>@ 1kHz                                                                                                                                                                                      |                                                         | -72<br>-70<br>-65<br>-63<br>11<br>0.8                                                              | -65<br>-62<br>-56<br>-54<br>12.6<br>1.5                            | -62<br>-60<br>-56<br>-54<br>13.5<br>1.9                             | -62<br>-60<br>-53<br>-54<br>14.1<br>2.3                          | dBc<br>dBc<br>dBc<br>dBc<br>nV/√Hz<br>pA/√Hz       | B<br>B           |

| STATIC DC PERFORMANCE input offset voltage average drift input bias current average drift input offset current power supply rejection ratio common-mode rejection ratio supply current open loop gain                      |                                                                                                                                                                                                                                                                                                                             | ±15, ±5<br>±15, ±5<br>±15, ±5<br>±15, ±5                | 1.5,1.5<br>6<br>1,1.2<br>4<br>0.1,0.1<br>95<br>110<br>2.3<br>85,80                                 | 5<br>-<br>3<br>-<br>1<br>75<br>75<br>4                             | 5<br>40<br>3<br>50<br>1<br>75<br>73<br>4                            | 5<br>70<br>4<br>70<br>3<br>75<br>70<br>4                         | mV C<br>μV/°C<br>μΑ °C<br>μΑ dB<br>dB dB<br>mA dB  | A<br>A<br>B<br>A |

| MISCELLANEOUS PERFORM input resistance input capacitance input voltage range input voltage range output voltage range output voltage range output ut resistance, closed loo output current sourcing output current sinking | $ \begin{array}{ll} common-mode \\ common-mode \\ differential-mode \\ common-mode \\ common-mode \\ R_L = 100\Omega \\ R_L = \infty \\ R_L = 100\Omega \\ R_L = \infty \end{array} $                                                                                                                                       | ##<br>25,5,<br>44,45,45,45,45,45,45,45,45,45,45,45,45,4 | 40<br>2<br>4.9<br>±12<br>±3<br>+11.6/-10.5<br>+13/-12.2<br>±2.8<br>±3.4<br>0.01<br>120,90<br>80,40 | 20<br>3<br>4.0<br>±11<br>+8.5/-8.5<br>+12/-12<br>0.05<br>100<br>75 | 15<br>3<br>3.0<br>±10.5<br>+8.5/-8.5<br>+12/-12<br>0.07<br>95<br>70 | 10<br>5<br>2.5<br>±10<br>+8.5/-8.5<br>+12/-12<br>0.1<br>90<br>65 | MΩ<br>pF<br>MΩ<br>V<br>V<br>V<br>V<br>V<br>O<br>mA |                  |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

| dotominoa nom tootoo parametera.                                                                                   |                                               |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Absolute Maximum                                                                                                   | Ratings                                       |

| supply voltage<br>maximum junction temperature<br>storage temperature range<br>lead temperature (soldering 10 sec) | ±18.0V<br>+150°C<br>-65°C to +150°C<br>+260°C |

| Notes                                                         |

|---------------------------------------------------------------|

| A) House area in 1000/ tented at 105°C comple tested at 185°C |

| A) J | -level: | spec is | 100% (6 | sieu ai - | +20 U, | Sample | 10210 |

|------|---------|---------|---------|-----------|--------|--------|-------|

| B) J | -level: | spec is | sample  | tested    | at +25 | 5°C.   |       |

| Ordering Information |                   |             |  |  |

|----------------------|-------------------|-------------|--|--|

| Model                | Temperature Range | Description |  |  |

| CLC436AJP            | -40°C to +85°C    | 8-pin PDIP  |  |  |

| CLC436AJE            | -40°C to +85°C    | 8-pin SOIC  |  |  |

| Package Thermal Resistance           |                   |                    |  |  |  |

|--------------------------------------|-------------------|--------------------|--|--|--|

| Package                              | θјс               | $\theta_{JA}$      |  |  |  |

| Plastic (AJP)<br>Surface Mount (AJE) | 90°C/W<br>120°C/W | 105°C/W<br>140°C/W |  |  |  |

**■** 6501124 0105133 18T ■

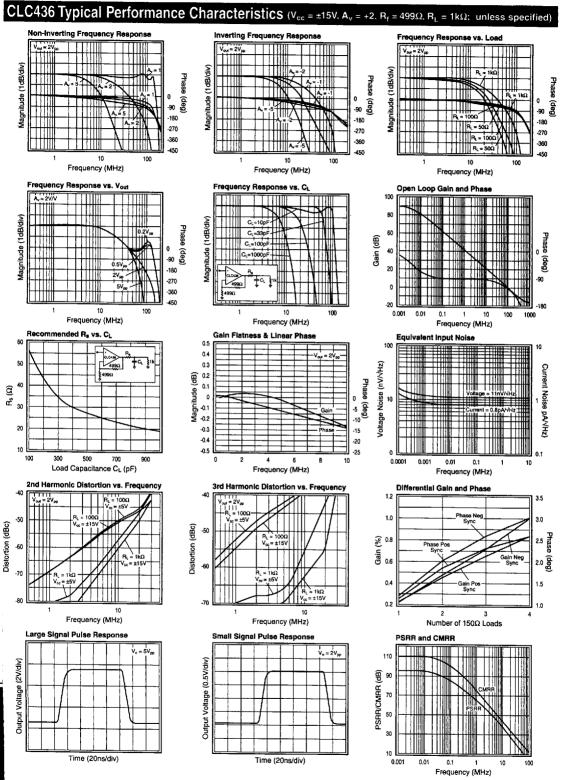

# CLC436 Typical Performance Characteristics (V<sub>cc</sub> = ±15V, A<sub>v</sub> = +2, R<sub>f</sub> = 499Ω, R<sub>L</sub> = 1kΩ; unless specified)

## **CLC436 OPERATION**

#### Description

The CLC436 is a unity gain stable voltage feedback amplifier. The voltage feedback topology allows for capacitors and nonlinear devices in the feedback path. The matched input bias currents track well over temperature. This allows the DC offset to be minimized by matching the impedance seen by both inputs.

The low cost, low power, conventional topology, and high output current make the CLC436 an excellent choice for applications such as:

- Low Power Cable Drivers

- Active Filters

- Buffers

- NTSC and PAL Video Systems

#### Gain

The non-inverting and inverting gain equations for the CLC436 are as follows:

Non-inverting Gain:

$$1 + \frac{R_f}{R_g}$$

Inverting Gain:  $-\frac{R_f}{R_a}$

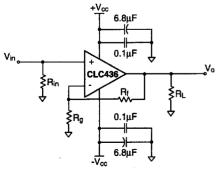

Where Rf is the feedback resistor and Rg is the gain setting resistor. Figure 1 shows the general noninverting gain configuration including the recommended bypass capacitors.

Figure 1: Recommended Non-Inverting Gain Circuit

#### **Output Drive Performance**

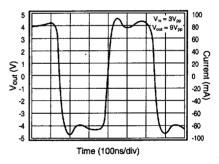

The CLC436 can source over 120mA of output current. It can easily drive  $9V_{pp}$  into a  $50\Omega$  load. The circuit shown in Figure 1 demonstrates the output current capability of the CLC436. The circuit values listed below, a 3Vpp input signal and ±15V supplies, were used to obtain the result shown in Figure 2.

- $\begin{array}{lll} \bullet & R_f = 499\Omega & \bullet & R_L = 50\Omega \\ \bullet & R_g = 249.5\Omega & \bullet & R_{in} = 50\Omega \end{array}$

Figure 2: Large Signal Pulse Response into 50Ω

The high output drive capability of the CLC436 is suitable for driving capacitive loads. When driving a capacitive load or coaxial cable, include a series resistance R<sub>s</sub> to improve stability. Refer to the R<sub>s</sub> vs Capacitive Load plot in the typical performance section to determine the recommended resistance for various capacitive loads.

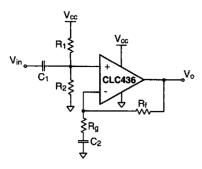

#### Single Supply Operation

The CLC436 can be operated from a single supply using the topology shown in Figure 3. R<sub>1</sub> and R<sub>2</sub> form a voltage divider that sets the non-inverting input DC voltage. The coupling capacitor C1 isolates the DC bias point from the previous stage. The DC gain of this circuit is 1 and the high frequency gain is set by R<sub>f</sub> and R<sub>o</sub>.

Figure 3: Single Supply Circuit

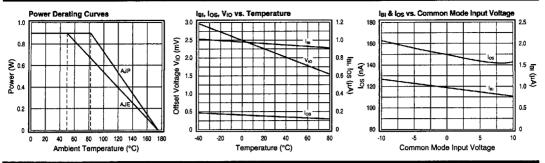

#### **Power Dissipation**

The power dissipation of an amplifier can be described in two conditions:

- Quiescent Power Dissipation Po (No Load Condition)

- Total Power Dissipation PT (with Load Condition)

The following steps can be taken to determine the power consumption of the CLC436:

- 1. Determine the quiescent power

- $P_Q = I_{cc} (V_{cc} V_{ee})$ 2. Determine the RMS power at the output stage

- $P_O = (V_{cc} V_{load}) (I_{load})$ 3. Determine the total RMS power  $P_T = P_O + P_O$

The maximum power that the package can dissipate at a given temperature is illustrated in the Power Derating plot in the Typical Performance Characteristics section. The power derating curve for any package can be derived by utilizing the following equation:

$$P = \frac{\left(175^{\circ} - T_{amb}\right)}{\theta_{JA}}$$

where: Tamb = Ambient temperature in °C  $\theta_{\text{JA}}$  = Thermal resistance, from junction to ambient, for a given package in °C/W

#### **Layout Considerations**

A proper printed circuit layout is essential for achieving high frequency performance. Comlinear provides evaluation boards for the CLC436 (730013 - DIP, 730027-SOIC) and suggests their use as a guide for high frequency layout and as an aid for device testing and characterization.

Supply bypassing is required for optimum performance. The bypass capacitors provide a low impedance current return path at the supply pins. They also provide high frequency filtering on the power supply traces. Other layout factors also play a major role in high frequency performance. The following steps are recommended as a basis for high frequency layout:

- 1. Include 6.8µF tantalum and 0.01µF ceramic bypass capacitors on both supplies.

- 2. Place the 6.8µF capacitors within 0.75 inches of the power pins.

- 3. Place the 0.01µF capacitors within 0.1 inches of the power pins.

- 4. Remove the ground plane near the input and output pins to reduce parasitic capacitance.

- 5. Minimize all trace lengths to reduce series inductances.

# **Applications Circuit**

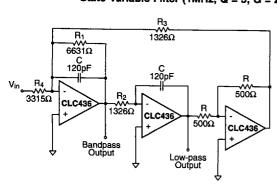

#### State Variable Filter

The filter shown on the front page offers both a bandpass and a low pass output. The design equations are shown below.

$$Q = \frac{R_1}{R_3}$$

$$A_v = \frac{R_1}{R_4}, \text{ desired mid-band gain}$$

$$f_r = \frac{Q}{2\pi R_1 C}, \text{ desired resonant frequency}$$

$$R_2 = R_3$$

The state variable filter can be modified to obtain a tunable band pass filter. This technique is shown in the CLC522, Wideband Variable Gain Amplifier. data sheet.

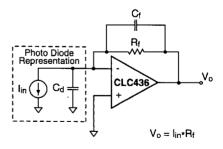

#### Transimpedance Application

The low 1.1pA√Hz input current noise and unity gain stability make the CLC436 useful as a photo diode preamplifier. Figure 4 illustrates a transimpedance amplifier. R<sub>f</sub> sets the transimpedance gain. The photodiode current is multiplied by R<sub>f</sub> to determine the output voltage.

Figure 4: Transimpedance Amplifier

The feedback capacitor (C<sub>f</sub>) is required to compensate for the added input capacitance of the photodiode (C<sub>d</sub>). The feedback capacitance reduces peaking in the frequency response. As the value of the feedback capacitance increases from zero, the rolloff of the response will increase.

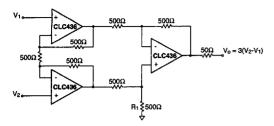

Instrumentation Amplifier

An instrumentation circuit is shown in Figure 5. The high CMRR of the CLC436 benefits this application. The resistors are kept equal to improve the overall CMRR.

Figure 5: Instrumentation Amplifier

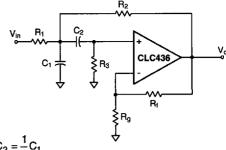

#### 2nd Order Sallen-Key Band-Pass Filter

The CLC436 is well suited for Sallen-Key type active filters. Figure 6 illustrates the band pass topology and design equations. For optimum high frequency performance:

- Keep the resistor values between  $10\Omega$  and  $1k\Omega$

- Keep the capacitor values between 10pF and 500pF

Begin design by choosing reasonable values for C<sub>1</sub> and C2 and then setting the desired mid-band gain.

$$C_2 = \frac{1}{5}C_1$$

$$G = 1 + \frac{R_f}{R_g}$$

, desired mid-band gain

$$R_1 = 2 \frac{Q}{GC_1(2\pi f)}$$

, where  $f =$  desired center frequency

$$R_2 = \frac{GR_1\left(\sqrt{1+4.8Q^2-2G+G^2}+1\right)}{4.8Q^2-2G+G^2}$$

$$R_3 = \frac{5GR_1\left(\sqrt{1+4.8Q^2-2G+G^2}+G-1\right)}{4Q^2}$$

Figure 6: Sallen-Key Active Filter