## WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEO002002A

### **General Specification**

| Item                 | Dimension               | Unit |  |  |  |

|----------------------|-------------------------|------|--|--|--|

| Number of Characters | 20 characters x 2 Lines |      |  |  |  |

| Module dimension     | 84.5 x 19.28 x 2.17     | mm   |  |  |  |

| View area            | 75.52 x 13.52           | mm   |  |  |  |

| Active area          | 73.52 x 11.52           | mm   |  |  |  |

| Dot size             | 0.62 x 0.67             | mm   |  |  |  |

| Dot pitch            | 0.65 x 0.70             | mm   |  |  |  |

| Character size       | 3.22 x 5.57             | mm   |  |  |  |

| Character pitch      | 3.70 x 5.95             | mm   |  |  |  |

| LCD type             | OLED, Monochrome        |      |  |  |  |

| Duty                 | 1/16                    |      |  |  |  |

| IC                   | SSD1311                 |      |  |  |  |

| Interface            | 6800, 8080, SPI, I2C    |      |  |  |  |

| Size                 | 2.93 inch               |      |  |  |  |

**N**\* WINSTAR

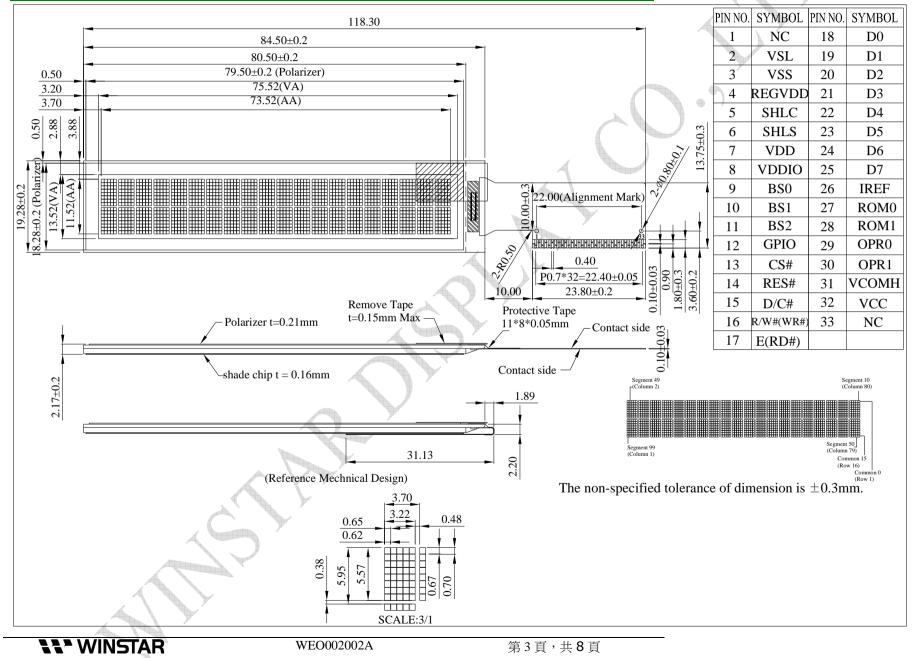

#### **Contour Drawing & Block Diagram**

### **Interface Pin Function**

| 8 VDD P   9 VDD P   1 SEG9 to SEG9 (Normal)   1 This pin is used to determine the Common output scanning direction.   2 SHLC I   1 This pin is used to determine the Common output scanning direction.   2 COM scan direction   3 SHLC I   1 COM scan direction   1 COM to COM31 (Normal)   0 COM31 to COM0 (Reverse)   Note (1) 0 is connected to VSS   (2) 1 is connected to VDDIO This pin is used to change the mapping between the display data column address and the Segment driver.   SEG scan direction I   1 SEG 0 to SEG99 (Normal)   0 SEG99 to SEG0 (Reverse)   Note (1) 0 is connected to VDDIO   7 VDD P   Power supply for core logic operation. VDD (vDD can be supplied externally or regulated internally.   1 SEG 10 (internal VDD is disabled), this is a power input pin.   1 SVDD (VD application (internal VDD is enabled), VDD is regulate internally from VDDIO.   7 VDD P   Power                                                                                                                                                                     | Pin No. | Symbol | Pin Type | Description                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| When external VSL is not used, this pin should be left open.<br>When external VSL is used, connect with resistor and diode to<br>ground (details depend on application).   3 VSS P   Ground pin. It must be connected to external ground.   4 REGVDD I   Internal VDD regulator selection pin in 5V I/O application mode<br>When this pin is pulled LOW, internal VDD regulator is disabled<br>(Low voltage I/O application).   5 SHLC I   1 This pin is used to determine the Common output scanning<br>direction.   COM scan direction I   1 COM scan direction   1 COM on COM31   6 SHLS   7 VDD   7 VDD   7 VDD   7 VDD   7 VDD   7 VDD   8 VDDIO   7 LOD   8 VDDIO                                                                                                                                                                                                                                                                                                                                                                                                          | 1       | NC     | —        | No connection                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 3 VSS P Ground pin. It must be connected to external ground.   4 REGVDD I Internal VDD regulator selection pin in 5V I/O application mode<br>When this pin is pulled HIGH, internal VDD regulator is disabled<br>(Low voltage I/O application).   5 SHLC I This pin is used to determine the Common output scanning<br>direction.   5 SHLC I This pin is used to determine the Common output scanning<br>direction.   6 SHLS I COM scan direction   1 COM scan direction I   0 COM to COM31 (Normal) 0   0 COM to COM31 (Normal) 0   0 Isconnected to VSS<br>(2) 1 is connected to VDDIO I   6 SHLS I This pin is used to change the mapping between the display data<br>column address and the Segment driver.   SEG scan direction 1 SEG to SEG9 (Normal)   0 SEG9 to SEG9 (Normal) 0   0 SEG9 to SEG9 (Normal) 0   0 SEG to SEG9 (Normal) 0   0 SEG9 to SEG9 (Normal) 0   0 SEG9 to SEG9 (Normal) 0   0 SEG9 to SEG9 (Normal) 0                                                                                                                                               | 2       | VSL    | Р        | When external VSL is not used, this pin should be left open.<br>When external VSL is used, connect with resistor and diode to                                                                                                                                                                                                                     |  |  |  |  |

| When this pin is pulled HIGH, internal VDD regulator is enabled (5V I/O application).   When this pin is pulled LOW, internal VDD regulator is disabled (Low voltage I/O application).   5 SHLC   I This pin is used to determine the Common output scanning direction.   COM scan direction SHLC   I COM scan direction   I COM scan direction   0 COM31 (Normal)   0 COM31 to COM0 (Reverse)   Note (1) 0 is connected to VSS   (2) 1 is connected to VDDIO SEG scan direction   SHLS I   This pin is used to change the mapping between the display data column address and the Segment driver.   SEG scan direction SEG scan direction   1 SEG to SEG99 (Normal)   0 SEG99 to SEG0 (Reverse)   Note (1) 0 is connected to VDDIO   7 VDD   P Power supply for core logic operation.   VDD can be supplication (internal VDD is disabled), this is a power input pin.   In LV 10 application (internal VDD is enabled), VDD is regulate internally from VDDIO.   A capacitor should be connected between VDD and VSS under a circumstances.   8 VDDIO   P                      | 3       | VSS    | Р        |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| a direction.   COM scan direction SHLC   COM scan direction 1   COM to COM31 (Normal)   0 COM31 to COM0   Reverse) Note   (1) 0 is connected to VSS (2) 1 is connected to VDDIO   6 SHLS I   This pin is used to change the mapping between the display data column address and the Segment driver.   SEG scan direction I   SEG scan direction I   1 SEG oto SEG99   Note (1) 0 is connected to VSS   (2) 1 is connected to VSS (2) 1 is connected to VDDIO   7 VDD P   Power supply for core logic operation. VDD can be supplied externally or regulated internally.   In LV IO application (internal VDD is disabled), this is a power input pin. In 5V IO application (internal VDD is enabled), VDD is regulate internally from VDDIO.   A capacitor should be connected between VDD and VSS under a circumstances. Revenus voltage I/O and 5V I/O application. It should match with the MCU interface voltage level and must be connected to external source.                                                                                                             | 4       | REGVDD | Ι        | When this pin is pulled LOW, internal VDD regulator is disabled                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 6 SHLS I This pin is used to change the mapping between the display data column address and the Segment driver. SEG scan direction   8 SHLS I SEG scan direction   1 SEG to SEG99 (Normal) Image: SEG scan direction   1 SEG to SEG99 (Normal) Image: SEG scan direction   1 SEG to SEG99 (Normal) Image: SEG scan direction   1 SEG to SEG99 (Normal) Image: SEG scan direction   1 SEG to SEG9 (Normal) Image: SEG scan direction   1 SEG to SEG99 (Normal) Image: SEG scan direction   1 SEG to SEG9 (Normal) Image: SEG scan direction   1 SEG to SEG9 (Normal) Image: SEG scan direction   1 SEG to SEG9 (Normal) Image: SEG scan direction   1 Image: SEG scan direction Image: SEG scan direction   1 Image: SEG scan direction Image: SEG scan direction   7 VDD P Power supply for core logic operation.   VDD can be supplied externally or regulated internally. In LV IO application (internal VDD is disabled), this is a power input pin.   In 5V IO application (internal VDD is enabled), VDD is regulated internally from VDDIO. A capacitor should be connecte | 5       | SHLC   | Ι        | This pin is used to determine the Common output scanning direction.   COM scan direction   SHLC COM scan direction   1 COM0 to COM31 (Normal)   0 COM31 to COM0 (Reverse)   Note (1) 0 is connected to VSS                                                                                                                                        |  |  |  |  |

| 7 VDD P Power supply for core logic operation.<br>VDD can be supplied externally or regulated internally.<br>In LV IO application (internal VDD is disabled), this is a power<br>input pin.<br>In 5V IO application (internal VDD is enabled), VDD is regulated<br>internally from VDDIO.<br>A capacitor should be connected between VDD and VSS under a<br>circumstances.   8 VDDIO P Low voltage power supply and power supply for interface logic<br>level in both Low Voltage I/O and 5V I/O application. It should<br>match with the MCU interface voltage level and must be<br>connected to external source.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6       | SHLS   | I        | SEG scan directionSHLSSEG direction1SEG0 to SEG99 (Normal)0SEG99 to SEG0 (Reverse)Note(1) 0 is connected to VSS                                                                                                                                                                                                                                   |  |  |  |  |

| level in both Low Voltage I/O and 5V I/O application. It should<br>match with the MCU interface voltage level and must be<br>connected to external source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7       | VDD    | Р        | Power supply for core logic operation.<br>VDD can be supplied externally or regulated internally.<br>In LV IO application (internal VDD is disabled), this is a power<br>input pin.<br>In 5V IO application (internal VDD is enabled), VDD is regulated<br>internally from VDDIO.<br>A capacitor should be connected between VDD and VSS under al |  |  |  |  |

| 9 BS0 I MCU bus interface selection pins. Select appropriate logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8       | VDDIO  | Р        | level in both Low Voltage I/O and 5V I/O application. It should match with the MCU interface voltage level and must be connected to external source.                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9       | BS0    | Ι        | MCU bus interface selection pins. Select appropriate logic                                                                                                                                                                                                                                                                                        |  |  |  |  |

**WINSTAR**

| 10           | BS1       |                                        | setting as described in the following table. BS2, BS1 and BS0 are   |

|--------------|-----------|----------------------------------------|---------------------------------------------------------------------|

| 11           | BS2       |                                        | pin select.                                                         |

|              | 0.02      |                                        | Bus Interface selection                                             |

|              |           |                                        | BS[2:0] Interface                                                   |

|              |           |                                        | 000 Serial Interface                                                |

|              |           |                                        | 001 Invalid                                                         |

|              |           |                                        | 010 I <sup>2</sup> C                                                |

|              |           |                                        | 011 Invalid                                                         |

|              |           |                                        | 100 8-bit 6800 parallel                                             |

|              |           |                                        | 101 4-bit 6800 parallel                                             |

|              |           |                                        | 110 8-bit 8080 parallel                                             |

|              |           |                                        | 111 4-bit 8080 parallel                                             |

|              |           |                                        | Note                                                                |

|              |           |                                        | (1) 0 is connected to VSS                                           |

|              |           |                                        | (2) 1 is connected to VDDIO                                         |

| 12           | GPIO      | I/O                                    | It is a GPIO pin. Details refer to OLED command DCh.                |

|              |           |                                        |                                                                     |

| 13           | CS#       | Ι                                      | This pin is the chip select input connecting to the MCU.            |

|              |           |                                        | The chip is enabled for MCU communication only when CS# is          |

|              |           |                                        | pulled LOW (active LOW).                                            |

|              |           |                                        | In I2C mode, this pin must be connected to VSS.                     |

| 14           | RES#      | Ι                                      | This pin is reset signal input.                                     |

|              | 112011    | -                                      | When the pin is pulled LOW, initialization of the chip is executed. |

|              |           |                                        | Keep this pin pull HIGH during normal operation.                    |

| 15           | D/C#      | Ι                                      | This pin is Data/Command control pin connecting to the MCU.         |

| 15           | $D/C\pi$  | I                                      |                                                                     |

|              |           |                                        | When the pin is pulled HIGH, the data at D[7:0] will be             |

|              |           |                                        | interpreted as data.                                                |

|              |           |                                        | When the pin is pulled LOW, the data at D[7:0] will be transferred  |

|              |           |                                        | to a command register.                                              |

|              |           |                                        | In I2C mode, this pin acts as SA0 for slave address selection.      |

|              |           |                                        | When serial interface is selected, this pin must be connected to    |

|              |           |                                        | VSS.                                                                |

| 16           | R/W#(WR#) |                                        | This pin is read / write control input pin connecting to the MCU    |

|              |           |                                        | interface.                                                          |

|              |           |                                        | When 6800 interface mode is selected, this pin will be used as      |

|              |           |                                        | Read/Write (R/W#) selection input. Read mode will be carried out    |

|              |           | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | when this pin is pulled HIGH and write mode when LOW.               |

|              |           | $\succ$                                | When 8080 interface mode is selected, this pin will be the Write    |

|              | $\frown$  |                                        | (WR#) input. Data write operation is initiated when this pin is     |

| A            |           |                                        |                                                                     |

|              |           |                                        | pulled LOW and the chip is selected.                                |

|              |           |                                        | When serial or I2C interface is selected, this pin must be          |

|              |           |                                        | connected to VSS.                                                   |

|              | ×         |                                        |                                                                     |

| V Y          |           |                                        |                                                                     |

| All advances |           |                                        |                                                                     |

|              |           |                                        |                                                                     |

|    | 17  | E(RD#)        | I   | This pin is MCU interface input.<br>When 6800 interface mode is selected, this pin will be used as the<br>Enable (E) signal.<br>Read/write operation is initiated when this pin is pulled HIGH and<br>the chip is selected.<br>When 8080 interface mode is selected, this pin receives the Read<br>(RD#) signal. Read operation is initiated when this pin is pulled<br>LOW and the chip is selected.<br>When serial or I2C interface is selected, this pin must be<br>connected to VSS. |  |  |  |  |

|----|-----|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    | 18  | D0            | I/O | These pins are bi-directional data bus connecting to the MCU data                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|    | 19  | D1            |     | bus.<br>Unused pins are recommended to tie LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|    | 20  | D2            |     | When serial interface mode is selected, D0 will be the serial clock                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|    | 21  | D3            |     | input: SCLK; D1 will be the serial data input: SID and D2 will be                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|    | 22  | D4            |     | the serial data output: SOD.<br>When I2C mode is selected, D2, D1 should be tied together and                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|    | 23  | D5            |     | serve as SDAout, SDAin in application and D0 is the serial clock                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|    | 23  | D6            |     | input, SCL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|    | 24  | D0<br>D7      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|    | 25  | IREF          | Ι   | This min is the segment estimat as ference min                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|    | 20  | IKEF          | 1   | This pin is the segment output current reference pin.<br>IREF is supplied externally.<br>A resistor should be connected between this pin and VSS to<br>maintain current of around 15uA.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|    | 27  | ROM0          | Ι   | These pins are used to select Character ROM; select appropriate                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|    | 28  | ROM1          | 4   | logic setting as described in the following table. ROM1 and<br>ROM0 are pin select as shown in below table:<br>Character ROM selection                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|    |     |               | S   | ROMI   ROM0   ROM     0   0   A     0   1   B     1   0   C     1   1   S/W selectable <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|    |     | $ \land \lor$ | S.  | (1) 0 is connected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    | 29  | OPR0          | Ι   | (2) 1 is connected to VDDIO<br>This pin is used to select the character number of character                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|    | 30  | OPR1          |     | generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| A  |     | 7             |     | Character RAM selection     OPR1   OPR0   CGROM   CGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|    | 7 + |               |     | 1 1 256 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    |     |               |     | 0 1 248 8<br>1 0 250 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| -4 |     |               |     | 0 0 240 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|    |     |               |     | Note<br>(1) 0 is connected to VSS<br>(2) 1 is connected to VDDIO                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

**WINSTAR**

| 31 | VCOMH | Р | COM signal deselected voltage level.                               |  |  |  |

|----|-------|---|--------------------------------------------------------------------|--|--|--|

|    |       |   | A capacitor should be connected between this pin and VSS.          |  |  |  |

|    |       |   | No external power supply is allowed to connect to this pin.        |  |  |  |

| 32 | VCC   | Р | Power supply for panel driving voltage. This is also the most      |  |  |  |

|    |       |   | positive power voltage supply pin. It is supplied by external high |  |  |  |

|    |       |   | voltage source.                                                    |  |  |  |

| 33 | NC    | _ | No connection                                                      |  |  |  |

|    |       |   |                                                                    |  |  |  |

۲

### **5.Absolute Maximum Ratings**

| Item                      | Symbol | Min  | Мах   | Unit |

|---------------------------|--------|------|-------|------|

| Supply Voltage For Logic  | VDD    | -0.3 | VDDIO | v    |

| Power Supply for I/O pins | VDDIO  | -0.3 | 6     | V    |

| Operating Voltage         | VCC    | 0    | 16    | V    |

| Operating Temperature     | TOP    | -40  | +80   | °C   |

| Storage Temperature       | TST    | -40  | +85   | °C   |

#### **Electrical Characteristics**

#### 6.1 DC Electrical Characteristics

| ltem                                 | Symbol | Condition                 | Min       | Тур  | Max       | Unit |

|--------------------------------------|--------|---------------------------|-----------|------|-----------|------|

|                                      | VDD    | Low Voltage I/O           | 2.8       | 3.0  | 3.3       | V    |

| Supply Voltage For Logic             |        | 5V I/O<br>(VDD as output) | —         |      | _         | V    |

| Power cupply for I/O pipe            | VDDIO  | Low Voltage I/O           | 2.8       | 3.0  | 3.3       | V    |

| Power supply for I/O pins            | VDDIO  | 5V I/O                    | 4.8       | 5.0  | 5.3       | V    |

| Operating Voltage                    | VCC    | —                         | 11.5      | 12.0 | 12.5      | V    |

| Input High Volt.                     | VIH    | —                         | 0.8xVDDIO | _    | _         | V    |

| Input Low Volt.                      | VIL    | —                         | —         | _    | 0.2xVDDIO | V    |

| Output High Volt.                    | VOH    | IOH=-0.5mA                | 0.9xVDDIO | _    | _         | V    |

| Output Low Volt.                     | VOL    | IOL=0.5mA                 | _         | _    | 0.1xVDDIO | V    |

| 50% Check Board<br>Operating Current | ICC    | VCC=12V                   | —         | 25   | 37.5      | mA   |